Le principali società tecnologiche tra cui AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung e TSMC hanno annunciato la formazione di un consorzio per sviluppare e implementare congiuntamente uno standard di interconnessione chiplet aperto, Universal Chiplet Interconnect Express (UCIe). Il risultato di questo lavoro è stata la prima versione della specifica UCIe 1.0.

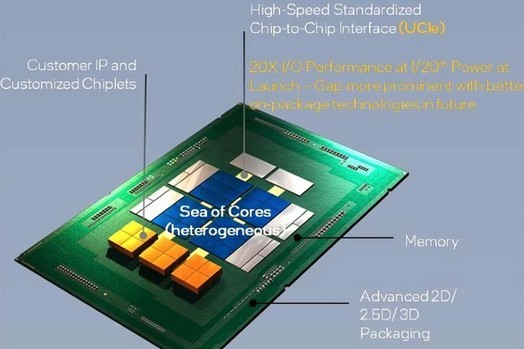

Lo scopo della norma è semplificare la possibilità di creare microcircuiti multi-chip utilizzando chip semiconduttori di diversi produttori. La specifica UCIe 1.0 standardizza le connessioni tra chip a livello fisico e logico e definisce, tra le altre cose, aspetti della loro implementazione come il protocollo elettrico, il modello software, la procedura di test di compatibilità, ecc. Il protocollo UCIe 1.0 si basa sugli standard di settore PCI Express e Compute Express Link.

Pertanto, i principali sviluppatori e produttori di semiconduttori si sono uniti per formare un unico ecosistema per la creazione di chip complessi, che, come previsto, in futuro, avranno principalmente un design multi-chip. Seguire la specifica UCIe 1.0 consentirà la progettazione gratuita di soluzioni combinate composte da chiplet di diversi sviluppatori, prodotte in diversi stabilimenti di semiconduttori utilizzando diversi processi tecnici.

La specifica UСIe 1.0 tiene conto dell'esistenza di vari pacchetti di chiplet, sia 2D standard che 2.5D più avanzati (utilizzando chip di connessione bridge). È ovvio che in futuro le specifiche si estenderanno a veri e propri chipset 3D.

L'utilizzo dei comuni protocolli PCIe e CXL a livello logico consente agli sviluppatori di ottenere connessioni flessibili e compatibili con elevata larghezza di banda e bassa latenza, che, in termini di velocità, sono adatte anche a lavorare con blocchi di memoria e I/O. Inoltre, la specifica UCIe presuppone la capacità di collegare dispositivi esterni ai chip, il che consente di organizzare le comunicazioni elettriche e ottiche con componenti esterni.

La specifica UCIe 1.0 definisce la velocità di trasferimento dei dati tra chip (da 4 a 32 miliardi di transazioni al secondo), la latenza (inferiore a 2 ns), la larghezza del bus (da 16 a 64 bit a seconda del pacchetto), la densità di contatto (distanza tra contatti da 25 a 130 µm) e la lunghezza dei conduttori di collegamento (fino a 25 mm). Naturalmente, i chipset 2.5D hanno indicatori di prestazioni più elevati, ma richiedono conduttori più corti. In generale, i chipset 2D hanno un limite di 125 GB/s per mm2, mentre i chipset 2.5D possono avere connessioni fino a 1350 GB/s per mm2 di area del die.

Vale la pena ricordare che Intel ha precedentemente proposto uno standard aperto per la connessione dei chiplet - Advanced Interconnect Bus (AIB) - che è ancora utilizzato in combinazione con la tecnologia EMIB. Ma non è compatibile con UCIe 1.0. Invece, il consorzio ha deciso di utilizzare più opzioni PCIe e CXL prodotte in serie, quindi successivamente Intel cambierà la sua implementazione delle connessioni inter-chip: l'azienda ha confermato di essere pronta per questo.

Il consorzio UCIe è aperto anche ad altre società che attualmente non ne fanno parte. Pertanto, Nvidia, che non è tra i fondatori di UCIe, potrà entrare a far parte del consorzio in un secondo momento.

2022-03-02 17:57:54

Autore: Vitalii Babkin