Führende Technologieunternehmen wie AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung und TSMC haben die Bildung eines Konsortiums zur gemeinsamen Entwicklung und Implementierung eines offenen Chiplet-Verbindungsstandards, Universal Chiplet Interconnect Express (UCIe), angekündigt. Das Ergebnis dieser Arbeit war die erste Version der UCIe 1.0-Spezifikation.

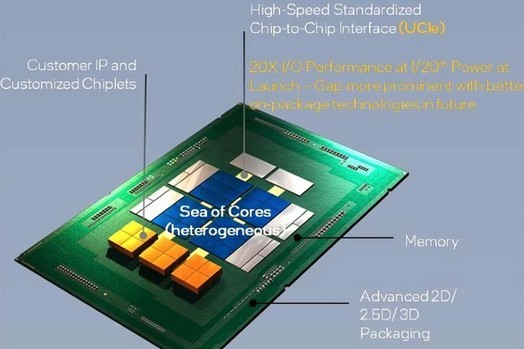

Der Zweck des Standards besteht darin, die Möglichkeit zu vereinfachen, Multi-Chip-Mikroschaltungen unter Verwendung von Halbleiterchips verschiedener Hersteller zu erstellen. Die Spezifikation UCIe 1.0 standardisiert Verbindungen zwischen Chips auf physikalischer und logischer Ebene und definiert unter anderem Aspekte ihrer Implementierung wie elektrisches Protokoll, Softwaremodell, Kompatibilitätstestverfahren usw. Das UCIe 1.0-Protokoll basiert auf den Industriestandards PCI Express und Compute Express Link.

Damit haben sich führende Entwickler und Hersteller von Halbleitern zu einem einzigen Ökosystem für die Erstellung komplexer Chips zusammengeschlossen, die erwartungsgemäß in Zukunft meist ein Multi-Chip-Design haben werden. Die Einhaltung der UCIe 1.0-Spezifikation ermöglicht die freie Gestaltung kombinierter Lösungen aus Chiplets verschiedener Entwickler, die in verschiedenen Halbleiterfabriken mit unterschiedlichen technischen Verfahren hergestellt werden.

Die UСIe 1.0-Spezifikation berücksichtigt die Existenz verschiedener Chiplet-Pakete - sowohl Standard-2D als auch fortschrittlicheres 2.5D (unter Verwendung von Brückenverbindungschips). Es liegt auf der Hand, dass die Spezifikation in Zukunft auf vollwertige 3D-Chipsätze ausgeweitet wird.

Die Verwendung gängiger PCIe- und CXL-Protokolle auf logischer Ebene ermöglicht Entwicklern flexible und kompatible Verbindungen mit hoher Bandbreite und geringer Latenz, die sich in Bezug auf die Geschwindigkeit auch für die Arbeit mit Speicher- und I/O-Blöcken eignen. Außerdem setzt die UCIe-Spezifikation die Fähigkeit voraus, Geräte außerhalb der Chips anzuschließen, wodurch Sie die elektrische und optische Kommunikation mit externen Komponenten organisieren können.

Die UCIe 1.0-Spezifikation definiert die Inter-Chip-Datenübertragungsrate (von 4 bis 32 Milliarden Transaktionen pro Sekunde), Latenz (weniger als 2 ns), Busbreite (von 16 bis 64 Bit je nach Paket), Kontaktdichte (Abstand zwischen Kontakte von 25 bis 130 µm) und die Länge der Anschlussleiter (bis 25 mm). Natürlich haben 2,5D-Chipsätze höhere Leistungsindikatoren, erfordern aber kürzere Leiter. Im Allgemeinen sind 2D-Chipsätze auf 125 GB/s pro mm2 begrenzt, während 2,5D-Chipsätze Verbindungen mit bis zu 1350 GB/s pro mm2 Chipfläche haben können.

Es sei daran erinnert, dass Intel zuvor einen offenen Standard für die Verbindung von Chiplets vorgeschlagen hat - Advanced Interconnect Bus (AIB) -, der immer noch in Verbindung mit der EMIB-Technologie verwendet wird. Aber es ist nicht mit UCIe 1.0 kompatibel. Stattdessen hat sich das Konsortium entschieden, mehr massenproduzierte PCIe- und CXL-Optionen zu verwenden, sodass Intel in der Folge seine Implementierung von Inter-Chip-Verbindungen ändern wird – das Unternehmen hat bestätigt, dass es dazu bereit ist.

Das UCIe-Konsortium steht auch anderen Unternehmen offen, die ihm derzeit nicht angehören. So kann Nvidia, das nicht zu den Gründern von UCIe gehört, dem Konsortium zu einem späteren Zeitpunkt beitreten.

2022-03-02 17:57:54

Autor: Vitalii Babkin