AMD, Arm, 구글, 인텔, 메타, 마이크로소프트, 퀄컴, 삼성, TSMC 등 주요 기술 기업들이 개방형 칩렛 상호 연결 표준인 UCIe(Universal Chiplet Interconnect Express)를 공동으로 개발 및 구현하기 위한 컨소시엄 구성을 발표했습니다. 이 작업의 결과는 UCIe 1.0 사양의 첫 번째 버전이었습니다.

이 표준의 목적은 다른 제조업체의 반도체 칩을 사용하여 다중 칩 마이크로 회로를 만드는 가능성을 단순화하는 것입니다. UCIe 1.0 사양은 물리적 및 논리적 수준에서 칩 간 연결을 표준화하고 무엇보다도 전기 프로토콜, 소프트웨어 모델, 호환성 테스트 절차 등과 같은 구현 측면을 정의합니다. UCIe 1.0 프로토콜은 업계 표준 PCI Express 및 Compute Express Link를 기반으로 합니다.

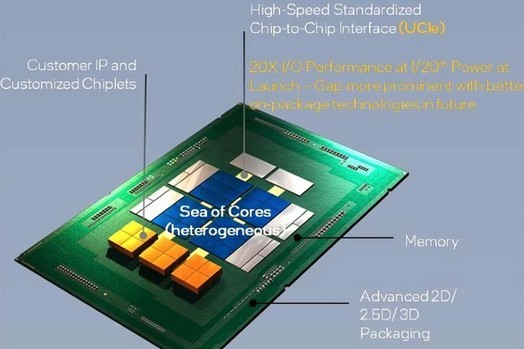

따라서 반도체의 주요 개발자와 제조업체가 함께 모여 복잡한 칩을 생성하기 위한 단일 생태계를 형성했으며, 예상대로 미래에는 대부분 다중 칩 설계를 갖게 될 것입니다. UCIe 1.0 사양을 따르면 서로 다른 기술 프로세스를 사용하여 서로 다른 반도체 공장에서 생산되는 서로 다른 개발자의 칩렛으로 구성된 결합 솔루션을 무료로 설계할 수 있습니다.

UСIe 1.0 사양은 표준 2D 및 고급 2.5D(브리지 연결 칩 사용)와 같은 다양한 칩렛 패키지의 존재를 고려합니다. 앞으로 사양이 본격적인 3D 칩셋으로 확대될 것은 자명하다.

논리적 수준에서 공통 PCIe 및 CXL 프로토콜을 사용하면 개발자가 높은 대역폭과 낮은 대기 시간으로 유연하고 호환 가능한 연결을 얻을 수 있으며, 이는 속도 면에서 메모리 및 I/O 블록 작업에도 적합합니다. 또한 UCIe 사양은 칩 외부의 장치를 연결하는 기능을 가정하므로 외부 구성 요소와 전기 및 광학 통신을 구성할 수 있습니다.

UCIe 1.0 사양은 칩 간 데이터 전송 속도(초당 40억 ~ 320억 트랜잭션), 대기 시간(2ns 미만), 버스 너비(패키지에 따라 16~64비트), 접촉 밀도( 25 ~ 130 µm의 접점) 및 연결 도체의 길이(최대 25 mm). 당연히 2.5D 칩셋은 성능 지표가 더 높지만 더 짧은 도체가 필요합니다. 일반적으로 2D 칩셋은 mm2당 125GB/s로 제한되는 반면 2.5D 칩셋은 다이 영역 mm2당 최대 1350GB/s까지 연결할 수 있습니다.

인텔이 이전에 칩렛 연결을 위한 개방형 표준인 AIB(Advanced Interconnect Bus)를 제안한 사실을 상기할 가치가 있습니다. 이 표준은 여전히 EMIB 기술과 함께 사용됩니다. 그러나 UCIe 1.0과 호환되지 않습니다. 대신 컨소시엄은 더 많은 대량 생산 PCIe 및 CXL 옵션을 사용하기로 결정했기 때문에 이후 Intel은 칩 간 연결 구현을 변경할 것입니다. 회사는 이에 대한 준비가 되었음을 확인했습니다.

UCIe 컨소시엄은 현재 소속되어 있지 않은 다른 회사에도 열려 있습니다. 따라서 UCIe의 창시자에 속하지 않는 Nvidia는 나중에 컨소시엄에 합류할 수 있습니다.

2022-03-02 17:57:54

작가: Vitalii Babkin