Des entreprises technologiques de premier plan, dont AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung et TSMC, ont annoncé la formation d'un consortium pour développer et mettre en œuvre conjointement une norme d'interconnexion de puces ouvertes, Universal Chiplet Interconnect Express (UCIe). Le résultat de ce travail a été la première version de la spécification UCIe 1.0.

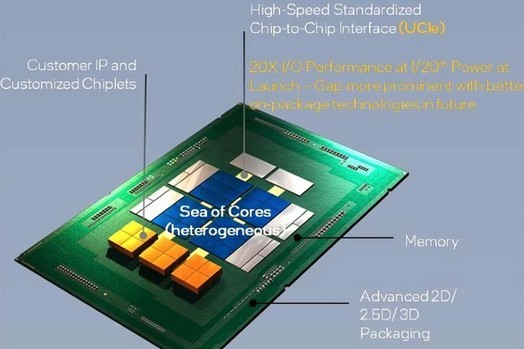

L'objectif de la norme est de simplifier la possibilité de créer des microcircuits multi-puces à l'aide de puces semi-conductrices de différents fabricants. La spécification UCIe 1.0 normalise les connexions inter-puces aux niveaux physique et logique et définit, entre autres, les aspects de leur mise en œuvre tels que le protocole électrique, le modèle logiciel, la procédure de test de compatibilité, etc. Le protocole UCIe 1.0 est basé sur les standards de l'industrie PCI Express et Compute Express Link.

Ainsi, les principaux développeurs et fabricants de semi-conducteurs se sont réunis pour former un écosystème unique pour la création de puces complexes, qui, comme prévu, à l'avenir, auront principalement une conception multi-puces. Le respect de la spécification UCIe 1.0 permettra la conception libre de solutions combinées composées de puces de différents développeurs, produites dans différentes usines de semi-conducteurs utilisant différents procédés techniques.

La spécification UСIe 1.0 prend en compte l'existence de divers packages de puces - à la fois 2D standard et 2.5D plus avancés (utilisant des puces de connexion de pont). Il est évident qu'à l'avenir, la spécification s'étendra à des chipsets 3D à part entière.

L'utilisation des protocoles communs PCIe et CXL au niveau logique permet aux développeurs d'obtenir des connexions flexibles et compatibles avec une bande passante élevée et une faible latence, qui, en termes de vitesse, conviennent également pour travailler avec de la mémoire et des blocs d'E / S. De plus, la spécification UCIe suppose la possibilité de connecter des appareils en dehors des puces, ce qui vous permet d'organiser des communications électriques et optiques avec des composants externes.

La spécification UCIe 1.0 définit le débit de transfert de données inter-puces (de 4 à 32 milliards de transactions par seconde), la latence (moins de 2 ns), la largeur de bus (de 16 à 64 bits selon les packages), la densité de contact (distance entre contacts de 25 à 130 µm) et la longueur des conducteurs de liaison (jusqu'à 25 mm). Naturellement, les chipsets 2.5D ont des indicateurs de performance plus élevés, mais nécessitent des conducteurs plus courts. En général, les chipsets 2D sont plafonnés à 125 Go/s par mm2, tandis que les chipsets 2,5D peuvent avoir des connexions jusqu'à 1350 Go/s par mm2 de surface de matrice.

Il convient de rappeler qu'Intel a déjà proposé un standard ouvert pour connecter les chiplets - Advanced Interconnect Bus (AIB) - il est toujours utilisé en conjonction avec la technologie EMIB. Mais il n'est pas compatible avec UCIe 1.0. Au lieu de cela, le consortium a décidé d'utiliser davantage d'options PCIe et CXL produites en série, de sorte qu'Intel modifiera ultérieurement sa mise en œuvre des connexions inter-puces - la société a confirmé qu'elle était prête pour cela.

Le consortium UCIe est également ouvert à d'autres entreprises qui n'en font pas partie actuellement. Ainsi, Nvidia, qui ne fait pas partie des fondateurs d'UCIe, pourra rejoindre le consortium ultérieurement.

2022-03-02 17:57:54

Auteur: Vitalii Babkin