AMD、Arm、Google、Intel、Meta、Microsoft、Qualcomm、Samsung、TSMCなどの主要なテクノロジー企業は、オープンチップレット相互接続規格であるUniversal Chiplet Interconnect Express(UCIe)を共同で開発および実装するためのコンソーシアムの設立を発表しました。この作業の結果は、UCIe1.0仕様の最初のバージョンでした。

この規格の目的は、さまざまなメーカーの半導体チップを使用してマルチチップマイクロ回路を作成する可能性を単純化することです。 UCIe 1.0仕様は、物理的および論理的レベルでチップ間接続を標準化し、とりわけ、電気プロトコル、ソフトウェアモデル、互換性テスト手順などの実装の側面を定義します。 UCIe 1.0プロトコルは、業界標準のPCIExpressおよびComputeExpressLinkに基づいています。

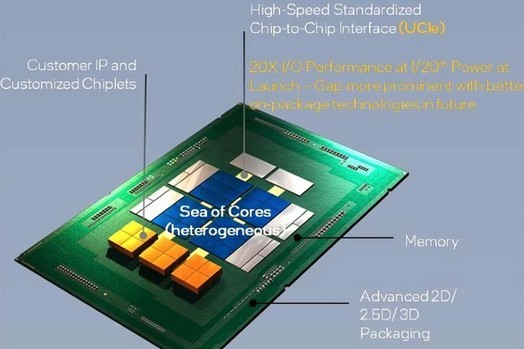

このように、半導体の主要な開発者とメーカーが集まって、複雑なチップを作成するための単一のエコシステムを形成しました。これは、予想どおり、将来的にはほとんどがマルチチップ設計になります。 UCIe 1.0仕様に従うと、さまざまな技術プロセスを使用してさまざまな半導体工場で製造された、さまざまな開発者からのチップレットで構成される複合ソリューションの無料設計が可能になります。

UСIe1.0仕様では、さまざまなチップレットパッケージの存在が考慮されています。標準の2Dとより高度な2.5D(ブリッジ接続チップを使用)の両方です。将来的には、仕様が本格的な3Dチップセットにまで拡大することは明らかです。

論理レベルで一般的なPCIeおよびCXLプロトコルを使用すると、開発者は高帯域幅と低遅延の柔軟で互換性のある接続を取得できます。これは、速度の観点から、メモリとI / Oブロックの操作にも適しています。また、UCIe仕様では、チップの外部にあるデバイスを接続できることを前提としています。これにより、外部コンポーネントとの電気的および光的通信を整理できます。

UCIe 1.0仕様では、チップ間データ転送速度(1秒あたり40〜320億トランザクション)、遅延(2 ns未満)、バス幅(パッケージに応じて、16〜64ビット)、接触密度(間の距離)が定義されています。 25〜130 µmの接点)および接続導体の長さ(最大25mm)。当然、2.5Dチップセットはより高いパフォーマンスインジケータを備えていますが、より短い導体が必要です。一般に、2Dチップセットの上限は125 GB / s / mm2ですが、2.5Dチップセットは最大1350 GB / s / mm2のダイ領域に接続できます。

Intelが以前にチップレットを接続するためのオープンスタンダードであるAdvancedInterconnect Bus(AIB)を提案したことを思い出してください。これは、現在でもEMIBテクノロジと組み合わせて使用されています。ただし、UCIe1.0とは互換性がありません。代わりに、コンソーシアムはより大量生産されたPCIeおよびCXLオプションを使用することを決定したため、その後Intelはチップ間接続の実装を変更します-同社はこれに対応できることを確認しました。

UCIeコンソーシアムは、現在その一部ではない他の企業にも開放されています。したがって、UCIeの創設者の1人ではないNvidiaは、後日コンソーシアムに参加できるようになります。

2022-03-02 17:57:54

著者: Vitalii Babkin