Come promesso alcuni anni fa, l'elemento costitutivo principale per la grafica e gli acceleratori Intel saranno i core Xe, che possono essere combinati in modo flessibile e abbinati ad altri blocchi hardware per ottenere le prestazioni e le funzionalità desiderate. La società ha già annunciato le prime "vere" GPU discrete della serie Arc e all'Intel Architecture Day ha condiviso i dettagli sugli acceleratori server Xe HPC e Ponte Vecchio.

Xe HPC si basa su Xe Core, che include otto motori vettoriali e matriciali rispettivamente per dati a 512 e 4096 bit. Condividono una cache L1 da 512 Kbyte con cui è possibile comunicare ad una velocità di 512 byte/ciclo.

Le prestazioni dichiarate per il motore vettoriale (ex UE), focalizzato sull'elaborazione "classica", sono 256 operazioni / ciclo per FP32 e FP64, o 512 - per FP16. Il motore a matrice è più necessario per i carichi AI, poiché funziona solo con dati TF32, FP16, BF16 e INT8 - rispettivamente 2048, 4096, 4096 e 8192 operazioni/ciclo. Questo motore funziona con le istruzioni XMX (Xe Matrix eXtensions), che sono in qualche modo simili a AMX in Intel Xeon Sapphire Rapids.

I singoli core sono combinati in "slice" - 16 Xe-Core ciascuno, integrati da 16 unità di ray tracing hardware. È la fetta che è il blocco funzionale di base. Viene prodotto presso TSMC utilizzando una tecnologia di processo a 5 nm come parte dell'iniziativa IDM 2.0 di Intel. Le fette sono combinate in pile - 4 pezzi. in tutti.

Lo stack include anche un "substrato" (o tile) di base (Base), quattro controller di memoria HBM2e (la memoria stessa è posizionata in tile separati), una cache L2 comune di 144 MB, un motore multimediale con codec hardware, nonché un riquadro Xe Link e un controller PCIe 5. Il riquadro di base è Intel 7 e utilizza EMIB per combinare tutti i blocchi.

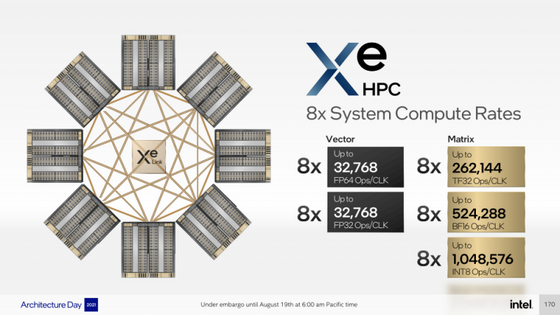

I riquadri Xe Link, prodotti utilizzando la tecnologia di processo a 7 nm di TSMC, includono 8 interfacce stack/acceleratore accoppiate con uno switch a 8 porte e utilizzano blocchi SerDes di classe 90G. Tutto ciò consente di combinare fino a 8 stack secondo lo schema one-to-one, che in generale ricorda l'approccio di NVIDIA, sebbene l'NVSwitch di quest'ultimo sia ancora (per ora) un componente esterno.

Nell'acceleratore stesso, a seconda della configurazione, possono esserci uno o due stack. Nel caso di Ponte Vecchio, sono solo due e Intel fornisce alcuni dati sulle sue prestazioni: più di 45 teraflop nei calcoli FP32, più di 5 TB/s di larghezza di banda del tessuto di memoria interna e più di 2 TB/s per collegamenti esterni. Per fare un confronto, NVIDIA A100 ha prestazioni dichiarate FP32 di 19,5 teraflop e AMD Instinct MI100 - 23,1 teraflop.

Intel ha anche mostrato i risultati del benchmark ResNet-50 nell'addestramento e nell'inferenza: rispettivamente 3400 e 43000 immagini al secondo. Questi risultati sono preliminari, poiché non sono stati ottenuti sulla versione finale di "silicon". Ma va tenuto presente che Ponte Vecchio ha un altro vantaggio: una tessera Rambo separata con una cache superveloce aggiuntiva, che può probabilmente essere considerata come una cache L3.

Nel complesso, il Ponte Vecchio è uno dei chip più complessi fino ad oggi. Combina l'utilizzo di piastrelle EMIB e Foveros 47 realizzate con cinque diversi processi tecnici e il budget totale dei transistor supera i 100 miliardi. Questi acceleratori saranno disponibili nel fattore di forma OAM e sotto forma di schede già pronte con quattro acceleratori a bordo (sempre , mi viene in mente NVIDIA HGX ). E sono proprio queste schede madri, abbinate a due processori Sapphire Rapids, che formeranno i nodi del supercomputer Aurora. Un'altra macchina che utilizzerà una serie di nuove CPU e acceleratori Intel sarà SuperMUC-NG (Fase 2).

Il rilascio ufficiale di Ponte Vecchio è previsto per il 2022, ma non sono lontani anche i rilasci delle prossime generazioni di acceleratori AMD e NVIDIA, con cui i nuovi prodotti dovranno essere confrontati. Finora, Intel è impegnata in una questione altrettanto importante: lo sviluppo di un ecosistema software, la cui base sarà oneAPI, un insieme di strumenti di sviluppo di applicazioni universali per applicazioni eterogenee (CPU, GPU, IPU, FPGA, ecc.), che è compatibile con l'hardware AMD e NVIDIA.

2021-08-19 15:25:15

Autore: Vitalii Babkin