Wie vor einigen Jahren versprochen, werden der Hauptbaustein für Intel-Grafik und -Beschleuniger Xe-Kerne sein, die flexibel kombiniert und mit anderen Hardware-Blöcken gepaart werden können, um die gewünschte Leistung und Funktionalität zu erreichen. Das Unternehmen hat bereits die ersten "echten" diskreten GPUs der Arc-Serie angekündigt und auf dem Intel Architecture Day Details zu den Serverbeschleunigern Xe HPC und Ponte Vecchio bekannt gegeben.

Xe HPC basiert auf dem Xe Core, der acht Vektor- und Matrix-Engines für 512 bzw. 4096 Bit Daten enthält. Sie teilen sich einen 512 KByte großen L1-Cache, mit dem Sie mit einer Geschwindigkeit von 512 Byte / Zyklus kommunizieren können.

Die angegebene Leistung für die Vektor-Engine (ehemals EU), die sich auf "klassisches" Computing konzentriert, beträgt 256 Operationen / Zyklus für FP32 und FP64 oder 512 - für FP16. Die Matrix-Engine wird mehr für KI-Lasten benötigt, da sie nur mit TF32-, FP16-, BF16- und INT8-Daten arbeitet - 2048, 4096, 4096 bzw. 8192 Operationen / Zyklus. Diese Engine arbeitet mit XMX-Anweisungen (Xe Matrix eXtensions), die AMX in Intel Xeon Sapphire Rapids etwas ähneln.

Die einzelnen Kerne werden zu „Slice“ zusammengefasst – jeweils 16 Xe-Cores, die durch 16 Hardware-Raytracing-Einheiten ergänzt werden. Das Slice ist der grundlegende Funktionsblock. Es wird bei TSMC mit einer 5-nm-Prozesstechnologie im Rahmen von Intels IDM 2.0-Initiative hergestellt. Scheiben werden zu Stapeln zusammengefasst - 4 Stk. bei jedem.

Der Stack enthält außerdem ein Basis-"Substrat" (oder eine Kachel), vier HBM2e-Speichercontroller (der Speicher selbst ist in separaten Kacheln untergebracht), einen gemeinsamen L2-Cache von 144 MB, eine Media Engine mit Hardware-Codecs sowie eine Xe-Link-Kachel und einen PCIe 5-Controller.Die Basis-Kachel ist Intel 7 und verwendet EMIB, um alle Blöcke zu kombinieren.

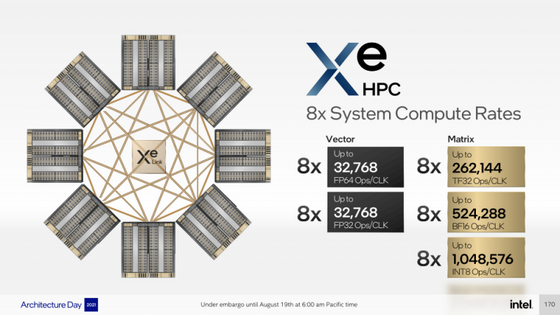

Xe Link-Kacheln, die mit der 7-nm-Prozesstechnologie von TSMC hergestellt werden, umfassen 8 Stack-/Beschleunigerschnittstellen, die mit einem 8-Port-Switch gekoppelt sind, und verwenden SerDes-Blöcke der Klasse 90G. All dies ermöglicht es Ihnen, bis zu 8 Stacks nach dem Eins-zu-Eins-Schema zu kombinieren, das im Allgemeinen dem Ansatz von NVIDIA ähnelt, obwohl dessen NVSwitch (vorerst) noch eine externe Komponente ist.

Im Beschleuniger selbst kann es je nach Konfiguration ein oder zwei Stacks geben. Im Fall von Ponte Vecchio sind es nur zwei, und Intel liefert einige Daten zu seiner Leistung: mehr als 45 Teraflops in FP32-Berechnungen, mehr als 5 TB / s interne Speicher-Fabric-Bandbreite und mehr als 2 TB / s für externe Anschlüsse. Zum Vergleich: NVIDIA A100 hat eine deklarierte FP32-Leistung von 19,5 Teraflops und AMD Instinct MI100 - 23,1 Teraflops.

Intel zeigte auch die Ergebnisse des ResNet-50-Benchmarks in Training und Inferenz: 3400 bzw. 43000 Bilder pro Sekunde. Diese Ergebnisse sind vorläufig, da sie nicht mit der endgültigen Version von "Silizium" erhalten wurden. Allerdings ist zu bedenken, dass Ponte Vecchio noch einen weiteren Vorteil hat – eine separate Rambo-Kachel mit einem zusätzlichen superschnellen Cache, der wohl als L3-Cache angesehen werden kann.

Insgesamt ist der Ponte Vecchio einer der komplexesten Chips bis heute. Es kombiniert mit EMIB und Foveros 47 Kacheln, die mit fünf verschiedenen technischen Verfahren hergestellt wurden, und das Gesamtbudget für Transistoren übersteigt 100 Milliarden. Diese Beschleuniger werden im OAM-Formfaktor und in Form von vorgefertigten Boards mit vier Beschleunigern an Bord (wieder , NVIDIA HGX fällt mir ein). Und genau solche Motherboards bilden zusammen mit zwei Sapphire Rapids-Prozessoren die Knoten des Supercomputers Aurora. Eine weitere Maschine, die eine Reihe neuer CPUs und Intel-Beschleuniger verwendet, wird SuperMUC-NG (Phase 2) sein.

Die offizielle Veröffentlichung von Ponte Vecchio ist für 2022 geplant, aber auch die Veröffentlichung der nächsten Generationen von AMD- und NVIDIA-Beschleunigern, mit denen die neuen Produkte verglichen werden müssen, sind nicht mehr weit. Bisher beschäftigt sich Intel mit einer ebenso wichtigen Angelegenheit - der Entwicklung eines Software-Ökosystems, dessen Grundlage oneAPI sein wird, ein Satz universeller Anwendungsentwicklungstools für heterogene (CPU, GPU, IPU, FPGA usw.) Anwendungen, die mit AMD- und NVIDIA-Hardware kompatibel ist.

2021-08-19 15:25:15

Autor: Vitalii Babkin