Comme promis il y a quelques années, le bloc de construction principal pour les graphiques et les accélérateurs Intel sera les cœurs Xe, qui peuvent être combinés de manière flexible et associés à d'autres blocs matériels pour obtenir les performances et les fonctionnalités souhaitées. La société a déjà annoncé les premiers « vrais » GPU discrets de la série Arc, et lors de la journée de l'architecture Intel, elle a partagé des détails sur les accélérateurs de serveur Xe HPC et Ponte Vecchio.

Xe HPC est basé sur le Xe Core, qui comprend huit moteurs vectoriels et matriciels pour des données de 512 et 4096 bits, respectivement. Ils partagent un cache L1 de 512 Ko avec lequel vous pouvez communiquer à une vitesse de 512 octets/cycle.

Les performances déclarées pour le moteur vectoriel (ex UE), axé sur le calcul "classique", sont de 256 opérations/cycle pour FP32 et FP64, ou 512 - pour FP16. Le moteur matriciel est plus nécessaire pour les charges AI, car il ne fonctionne qu'avec les données TF32, FP16, BF16 et INT8 - respectivement 2048, 4096, 4096 et 8192 opérations/cycle. Ce moteur fonctionne avec des instructions XMX (Xe Matrix eXtensions), qui sont quelque peu similaires à AMX dans Intel Xeon Sapphire Rapids.

Les cœurs individuels sont combinés en "tranche" - 16 Xe-Cores chacun, qui sont complétés par 16 unités de lancer de rayons matérielles. C'est la tranche qui est le bloc fonctionnel de base. Il est fabriqué chez TSMC à l'aide d'une technologie de processus de 5 nm dans le cadre de l'initiative IDM 2.0 d'Intel. Les tranches sont combinées en piles - 4 pièces. en tout le monde.

La pile comprend également un "substrat" (ou tuile) de base (Base), quatre contrôleurs de mémoire HBM2e (la mémoire elle-même est placée dans des tuiles séparées), un cache L2 commun de 144 Mo, un moteur multimédia avec des codecs matériels, ainsi que une tuile Xe Link et un contrôleur PCIe 5. La tuile de base est Intel 7 et utilise EMIB pour combiner tous les blocs.

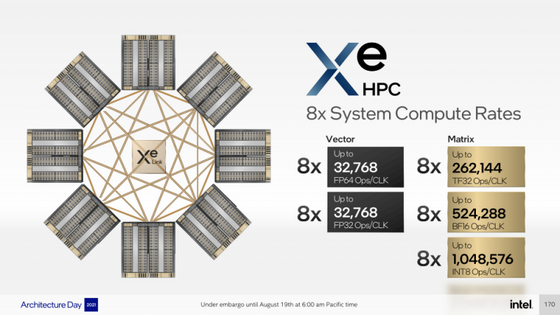

Les dalles Xe Link, fabriquées à l'aide de la technologie de traitement 7 nm de TSMC, comprennent 8 interfaces de pile/accélérateur couplées à un commutateur à 8 ports et utilisent des blocs SerDes de classe 90G. Tout cela permet de combiner jusqu'à 8 stacks selon le schéma one-to-one, qui, en général, ressemble à l'approche de NVIDIA, bien que le NVSwitch de ce dernier soit toujours (pour l'instant) un composant externe.

Dans l'accélérateur lui-même, selon la configuration, il peut y avoir une ou deux piles. Dans le cas du Ponte Vecchio, il n'y en a que deux, et Intel fournit quelques données sur ses performances : plus de 45 téraflops dans les calculs FP32, plus de 5 To/s de bande passante de mémoire interne et plus de 2 To/s pour connexions externes. À titre de comparaison, NVIDIA A100 a une performance FP32 déclarée de 19,5 téraflops et AMD Instinct MI100 - 23,1 téraflops.

Intel a également montré les résultats du benchmark ResNet-50 en matière d'entraînement et d'inférence : 3 400 et 43 000 images par seconde, respectivement. Ces résultats sont préliminaires, puisqu'ils n'ont pas été obtenus sur la version finale du « silicium ». Mais il faut garder à l'esprit que Ponte Vecchio a un autre avantage - une tuile Rambo séparée avec un cache ultra-rapide supplémentaire, qui peut probablement être considéré comme un cache L3.

Globalement, le Ponte Vecchio est l'une des puces les plus complexes à ce jour. Il combine l'utilisation de tuiles EMIB et Foveros 47 fabriquées à l'aide de cinq procédés techniques différents, et le budget total des transistors dépasse 100 milliards. Ces accélérateurs seront disponibles au format OAM et sous forme de cartes prêtes à l'emploi avec quatre accélérateurs intégrés (encore une fois , NVIDIA HGX vient à l'esprit). Et ce sont précisément de telles cartes mères, associées à deux processeurs Sapphire Rapids, qui formeront les nœuds du supercalculateur Aurora. Une autre machine utilisant un tas de nouveaux processeurs et accélérateurs Intel sera SuperMUC-NG (Phase 2).

La sortie officielle du Ponte Vecchio est prévue pour 2022, mais la sortie des prochaines générations d'accélérateurs AMD et NVIDIA, avec lesquelles il faudra comparer les nouveaux produits, n'est pas loin non plus. Jusqu'à présent, Intel est engagé dans un dossier tout aussi important - le développement d'un écosystème logiciel, dont la base sera oneAPI, un ensemble d'outils de développement d'applications universels pour des applications hétérogènes (CPU, GPU, IPU, FPGA, etc.), qui est compatible avec le matériel AMD et NVIDIA.

2021-08-19 15:25:15

Auteur: Vitalii Babkin