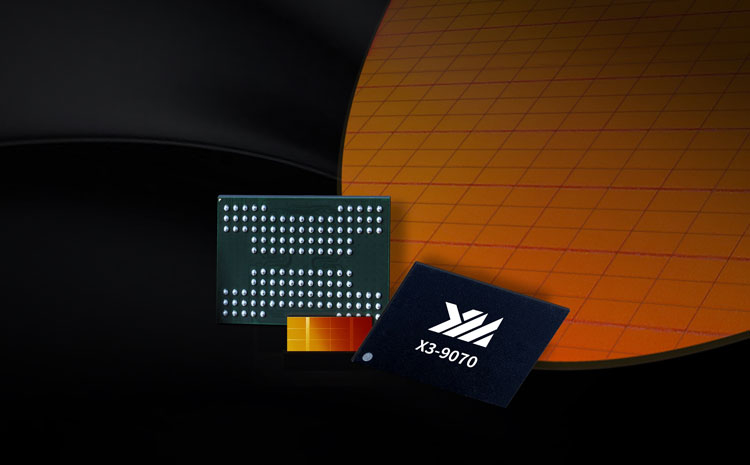

Oggi al Flash Memory Summit (FMS) 2022, l'YMTC cinese ha presentato la memoria flash NAND 3D X3-9070 basata sull'innovativa architettura Xtacking 3.0. I nuovi chip 3D NAND cinesi saranno in grado di fornire maggiore velocità ed efficienza.

L'architettura Xtacking è stata introdotta nel 2018 e da allora si è evoluta alla terza generazione. Si presuppone che una matrice di celle di memoria NAND 3D si trovi su un chip separato e che i circuiti di alimentazione e di controllo siano posizionati sull'altro. Array e controller possono essere prodotti utilizzando diversi processi tecnici, poiché il primo e il secondo sono realizzati su wafer di silicio diversi. Successivamente, il chip di controllo viene combinato con array di celle di memoria e l'output è un chip di memoria NAND 3D completo.

La produzione separata di celle e controller consente di risparmiare spazio sul piano dei cristalli di memoria (produrre più celle da ciascuna piastra), nonché di aggiornare celle o controller senza essere vincolati alla produzione dell'uno e dell'altro. Al momento, il secondo scenario è in fase di implementazione, quando YMTC si prepara a rilasciare una NAND 3D più produttiva senza cambiare la tecnologia per la produzione di array di memoria.

Poiché si tratta di migliorare la logica e la potenza, lo sviluppatore non ha dedicato una sola riga al raggiungimento di questo o quel record nella produzione di più livelli NAND 3D, come hanno fatto, ad esempio, Micron e SK hynix, che hanno annunciato il rilascio di 232 - e 238-, rispettivamente, memoria NAND 3D a strati. Invece, YMTC ha riferito che le prestazioni dei nuovi chip abilitati Xtacking 3.0 raggiungono velocità di I/O fino a 2400 MT/s per pin. Dichiara inoltre di essere compatibile con l'interfaccia ONFI 5.0 e di ottenere prestazioni migliori del 50% rispetto alla generazione precedente di prodotti.

Inoltre, l'X3-9070 è il prodotto flash con la densità più alta nella storia dell'YMTC, offrendo 1 TB di capacità di archiviazione in un monoblocco ultra compatto. Il nuovo controller ora supporta l'organizzazione delle celle flash a 6 piani, mentre in precedenza era supportata l'organizzazione a 4 piani. Il supporto per 6 aree di celle per l'elaborazione indipendente consente di espandere le operazioni parallele e aumentare le prestazioni della memoria. In particolare, la produttività promette di crescere fino al 50% riducendo i consumi fino al 25%.

Inoltre, l'azienda non specifica quando la nuova architettura apparirà nei suoi prodotti.

2022-08-03 12:36:08

Autore: Vitalii Babkin