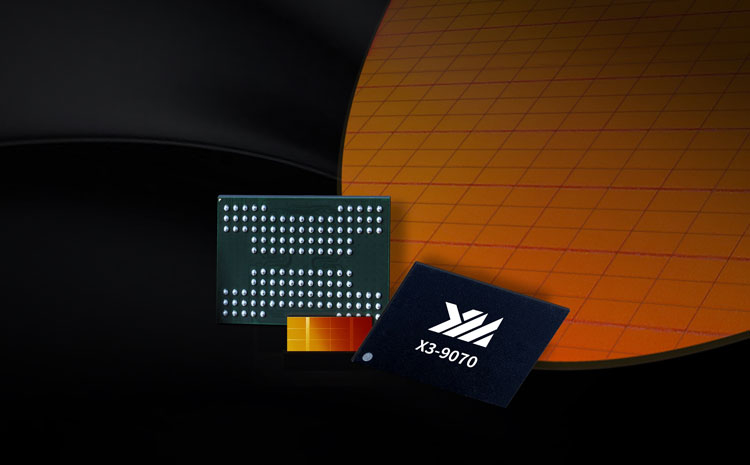

Aujourd'hui, lors du Flash Memory Summit (FMS) 2022, le YMTC chinois a dévoilé la mémoire flash NAND 3D X3-9070 basée sur l'architecture innovante Xtacking 3.0. Les nouvelles puces NAND 3D chinoises seront en mesure de fournir une vitesse et une efficacité plus élevées.

L'architecture Xtacking a été introduite en 2018 et a depuis évolué vers la troisième génération. Il suppose qu'un réseau de cellules de mémoire NAND 3D est situé sur une puce séparée et que les circuits d'alimentation et de contrôle sont placés sur l'autre. Les matrices et les contrôleurs peuvent être produits à l'aide de différents procédés techniques, puisque le premier et le second sont réalisés sur des tranches de silicium différentes. Par la suite, la puce de contrôle est combinée avec des matrices de cellules de mémoire, et la sortie est une puce de mémoire 3D NAND complète.

La production séparée de cellules et de contrôleurs vous permet d'économiser de l'espace sur le plan des cristaux de mémoire (produisez plus de cellules à partir de chaque plaque), ainsi que de mettre à niveau des cellules ou des contrôleurs sans être lié à la production de l'un et de l'autre. À l'heure actuelle, le deuxième scénario est en cours de mise en œuvre, lorsque YMTC se prépare à publier une NAND 3D plus productive sans changer la technologie de production de matrices de mémoire.

Puisque nous parlons d'amélioration de la logique et de la puissance, le développeur n'a pas consacré une seule ligne à atteindre tel ou tel record dans la production de plusieurs couches 3D NAND, comme l'ont fait, par exemple, Micron et SK hynix, qui ont annoncé la sortie de 232 - et 238-, respectivement mémoire NAND 3D en couches. Au lieu de cela, YMTC a signalé que les performances des nouvelles puces compatibles Xtacking 3.0 atteignent des vitesses d'E/S allant jusqu'à 2 400 MT/s par broche. Il prétend également être compatible avec l'interface ONFI 5.0 et atteindre des performances 50% supérieures à celles de la génération précédente de produits.

De plus, le X3-9070 est le produit flash à la plus haute densité de l'histoire de YMTC, offrant 1 To de capacité de stockage dans un monobloc ultra-compact. Le nouveau contrôleur prend désormais en charge l'organisation des cellules flash à 6 plans, alors que l'organisation à 4 plans était auparavant prise en charge. La prise en charge des zones à 6 cellules pour un traitement indépendant vous permet d'étendre les opérations parallèles et d'augmenter les performances de la mémoire. En particulier, la productivité promet de croître jusqu'à 50 % tout en réduisant la consommation jusqu'à 25 %.

De plus, la société ne précise pas quand la nouvelle architecture apparaîtra dans ses produits.

2022-08-03 12:36:08

Auteur: Vitalii Babkin