L'architettura RISC-V è piuttosto giovane ed è solitamente associata a chip economici su schede come il Raspberry Pi. Tuttavia, tecnicamente, consente anche di creare potenti processori in grado di competere con le migliori soluzioni basate sulle architetture Arm e x86. Al vertice RISC-V, Ventana Micro Systems ha annunciato un'intera famiglia di processori ad alte prestazioni, il primo dei quali è stato il chip Veyron V1, che, secondo gli sviluppatori, sarà in grado di competere nelle prestazioni single-thread con l'ultimo CPU di fascia alta.

La novità è rivolta al mercato degli hyperscaler e, grazie al design del chiplet, il nuovo processore è stato originariamente sviluppato come personalizzabile per le attività dei clienti. Veyron V1 sarà offerto sotto forma di una sorta di kit-costruttore, che include uno o più chiplet informatici Veyron, un hub I/O e un'interconnessione che consente di collegare insieme tutti i componenti. Questo, secondo gli sviluppatori, dovrebbe accelerare e ridurre seriamente il costo dell'introduzione di una nuova piattaforma di processore, riducendo i costi di sviluppo del chip del 75% e il tempo di creazione a non più di due anni.

Il chiplet di calcolo Veyron V1 utilizza core RISC-V avanzati a 64 bit e dispone di 2 MB di cache L2, oltre a un controller di memoria multi-thread. Le configurazioni chiplet sono disponibili con 6, 8, 12 o 16 core a circa 3 GHz, che è paragonabile alle soluzioni Google e AWS. Il processore può essere utilizzato non solo nel data center, ma anche in vari sistemi embedded, stazioni base 5G o persino workstation client.

Il design architettonico della Veyron V1 utilizza una conduttura aggressiva a otto stadi, fuori servizio. Il chip è in grado di funzionare fino a 3,6 GHz utilizzando la tecnologia di processo a 5 nm di TSMC. L'hub I/O può essere realizzato utilizzando processi più economici a 12 nm o addirittura a 16 nm. È stata sviluppata una speciale interconnessione D2D a bassa latenza per collegare i componenti del processore.

Ogni chiplet include fino a 16 core e il processore può essere scalato fino a 192 core in 12 chiplet. La cache L3 condivisa totale è di 48 MB. Viene dichiarato un elevato livello di protezione dell'architettura contro gli attacchi attraverso canali di terze parti. Gli sviluppatori affermano un basso consumo energetico senza precedenti: 128 core V1 si adatteranno a 280 W; AMD EPYC 7763 consuma la stessa quantità con la metà del numero di core.

L'annuncio di Ventana non può essere definito "cartaceo": l'azienda parla della disponibilità di kit per sviluppatori, inoltre, in due tipi di chassis contemporaneamente: in un desktop e in uno chassis per server 2U. La configurazione include 16 core V1, DDR5 da 128 GB collegati tramite interfaccia CXL (PCIe 5.0) x16, due slot di espansione PCIe 5.0 x16 liberi, unità di avvio NVMe M.2 e 8 porte SSD 1GbE NVMe SFF da 2,5" per la gestione remota.

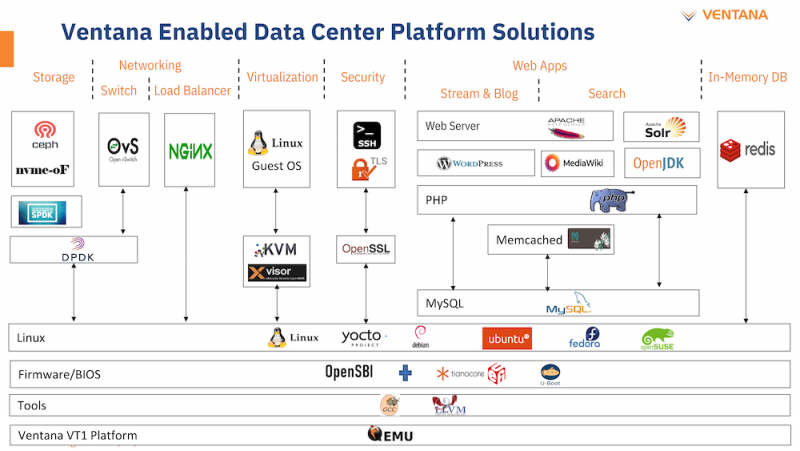

L'azienda non ha dimenticato nemmeno il supporto software: le piattaforme per sviluppatori Ventana Veyron V1 saranno accompagnate da un vero e proprio SDK con il software principale già portato sulla nuova architettura. L'elenco include i compilatori GCC e LLVM, il debugger OpenOCD/GDB, le sorgenti e i file binari del caricatore U-Boot e Tianocore UEFI EDK2.1. Sono supportate numerose distribuzioni Linux, così come altri software di sistema e applicativi. I nuovi sistemi dovrebbero essere disponibili all'inizio del prossimo anno.

2022-12-14 08:08:37

Autore: Vitalii Babkin

URL di origine