L'architecture RISC-V est assez jeune et est généralement associée à des puces économiques sur des cartes comme le Raspberry Pi. Cependant, techniquement, cela permet aussi de créer des processeurs puissants pouvant rivaliser avec les meilleures solutions basées sur les architectures Arm et x86. Lors du sommet RISC-V, Ventana Micro Systems a annoncé toute une famille de processeurs hautes performances, dont le premier était la puce Veyron V1, qui, selon les développeurs, pourra rivaliser en performances monothread avec les dernières processeurs haut de gamme.

La nouveauté est destinée au marché des hyperscalers, et grâce à la conception du chiplet, le nouveau processeur a été initialement développé comme personnalisable pour les tâches des clients. Veyron V1 sera proposé sous la forme d'une sorte de kit-constructeur, qui comprend un ou plusieurs chiplets de calcul Veyron, un hub d'E/S et une interconnexion qui permet de connecter tous les composants entre eux. Ceci, selon les développeurs, devrait sérieusement accélérer et réduire le coût d'introduction d'une nouvelle plate-forme de processeur, réduisant les coûts de développement de puces de 75% et le temps de création à pas plus de deux ans.

Le chiplet de calcul Veyron V1 utilise des cœurs RISC-V 64 bits avancés et dispose de 2 Mo de cache L2, ainsi que d'un contrôleur de mémoire multithread. Les configurations de chiplet sont disponibles avec 6, 8, 12 ou 16 cœurs à environ 3 GHz, ce qui est comparable aux solutions Google et AWS. Le processeur peut être utilisé non seulement dans le centre de données, mais également dans divers systèmes embarqués, stations de base 5G ou même postes de travail clients.

La conception architecturale du Veyron V1 utilise un pipeline agressif à huit étages, hors service. La puce est capable de fonctionner jusqu'à 3,6 GHz en utilisant la technologie de traitement 5 nm de TSMC. Le concentrateur d'E / S peut être fabriqué à l'aide de processus 12 nm ou même 16 nm moins chers. Une interconnexion D2D spéciale à faible latence a été développée pour connecter les composants du processeur.

Chaque chiplet comprend jusqu'à 16 cœurs, et le processeur peut être mis à l'échelle jusqu'à 192 cœurs dans 12 chiplets. Le cache L3 partagé total est de 48 Mo. Un haut niveau de protection de l'architecture contre les attaques via des canaux tiers est déclaré. Les développeurs revendiquent une faible consommation d'énergie sans précédent : 128 cœurs V1 s'intégreront dans 280 W ; AMD EPYC 7763 consomme la même quantité avec la moitié du nombre de cœurs.

L'annonce de Ventana ne peut pas être qualifiée de "papier" - la société parle de la disponibilité de kits de développement, d'ailleurs, dans deux types de châssis à la fois : dans un châssis de bureau et dans un châssis de serveur 2U. La configuration comprend 16 cœurs V1, 128 Go DDR5 connectés via une interface CXL (PCIe 5.0) x16, deux emplacements d'extension PCIe 5.0 x16 libres, un lecteur de démarrage NVMe M.2 et 8 ports NVMe SFF 2,5" SSD 1GbE pour la gestion à distance.

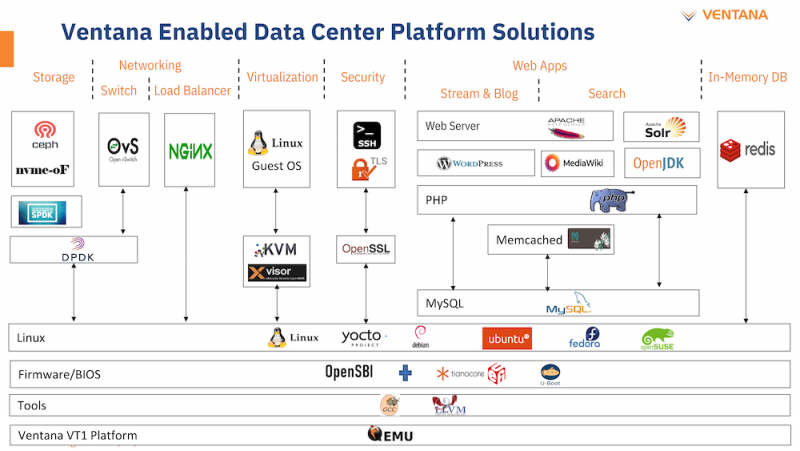

L'entreprise n'a pas non plus oublié le support logiciel : les plates-formes de développement Ventana Veyron V1 seront accompagnées d'un SDK à part entière avec les principaux logiciels déjà portés sur la nouvelle architecture. La liste comprend les compilateurs GCC et LLVM, le débogueur OpenOCD/GDB, les sources et les binaires du chargeur U-Boot et Tianocore UEFI EDK2.1. Un certain nombre de distributions Linux sont prises en charge, ainsi que d'autres logiciels système et d'application. Les nouveaux systèmes devraient être disponibles au début de l'année prochaine.

2022-12-14 08:08:37

Auteur: Vitalii Babkin

URL source