Die RISC-V-Architektur ist recht jung und wird normalerweise mit kostengünstigen Chips auf Platinen wie dem Raspberry Pi in Verbindung gebracht. Technisch gesehen ermöglicht es Ihnen jedoch auch, leistungsstarke Prozessoren zu erstellen, die mit den besten Lösungen auf Basis der Arm- und x86-Architekturen konkurrieren können. Auf dem RISC-V-Gipfel kündigte Ventana Micro Systems eine ganze Familie von Hochleistungsprozessoren an, deren erster der Veyron V1-Chip war, der laut den Entwicklern in Sachen Single-Thread-Leistung mit den neuesten mithalten kann High-End-CPUs.

Die Neuheit richtet sich an den Hyperscaler-Markt, und dank des Chiplet-Designs wurde der neue Prozessor ursprünglich als anpassbar für Kundenaufgaben entwickelt. Veyron V1 wird in Form einer Art Baukasten angeboten, der ein oder mehrere Veyron-Rechenchiplets, einen E/A-Hub und eine Verbindung enthält, mit der Sie alle Komponenten miteinander verbinden können. Laut den Entwicklern sollte dies die Einführung einer neuen Prozessorplattform erheblich beschleunigen und die Kosten senken, die Chipentwicklungskosten um 75 % und die Erstellungszeit auf nicht mehr als zwei Jahre reduzieren.

Das Veyron V1-Rechenchiplet verwendet fortschrittliche 64-Bit-RISC-V-Kerne und verfügt über 2 MB L2-Cache sowie einen Multithread-Speichercontroller. Chiplet-Konfigurationen sind mit 6, 8, 12 oder 16 Kernen bei etwa 3 GHz erhältlich, was mit Google- und AWS-Lösungen vergleichbar ist. Der Prozessor kann nicht nur im Rechenzentrum, sondern auch in verschiedenen eingebetteten Systemen, 5G-Basisstationen oder sogar Client-Workstations verwendet werden.

Das architektonische Design des Veyron V1 verwendet eine achtstufige, ungeordnete, aggressive Pipeline. Der Chip kann mit der 5-nm-Prozesstechnologie von TSMC mit bis zu 3,6 GHz betrieben werden. Der I/O-Hub kann mit billigeren 12-nm- oder sogar 16-nm-Prozessen hergestellt werden. Zur Verbindung der Prozessorkomponenten wurde eine spezielle D2D-Verbindung mit niedriger Latenz entwickelt.

Jedes Chiplet umfasst bis zu 16 Kerne, und der Prozessor kann auf bis zu 192 Kerne in 12 Chiplets skaliert werden. Der gemeinsam genutzte L3-Cache beträgt insgesamt 48 MB. Es wird ein hohes Schutzniveau der Architektur gegen Angriffe über Drittkanäle deklariert. Die Entwickler beanspruchen einen beispiellos geringen Stromverbrauch: 128 V1-Kerne passen in 280 W; AMD EPYC 7763 verbraucht bei halber Kernzahl die gleiche Menge.

Die Ankündigung von Ventana kann nicht als "Papier" bezeichnet werden - das Unternehmen spricht über die Verfügbarkeit von Entwicklerkits, außerdem in zwei Arten von Gehäusen gleichzeitig: in einem Desktop- und in einem 2U-Servergehäuse. Die Konfiguration umfasst V1 mit 16 Kernen, 128 GB DDR5, verbunden über CXL (PCIe 5.0) x16-Schnittstelle, zwei freie PCIe 5.0 x16-Erweiterungssteckplätze, NVMe M.2-Startlaufwerk und 8 NVMe SFF 2,5-Zoll-SSD-1-GbE-Ports für die Fernverwaltung.

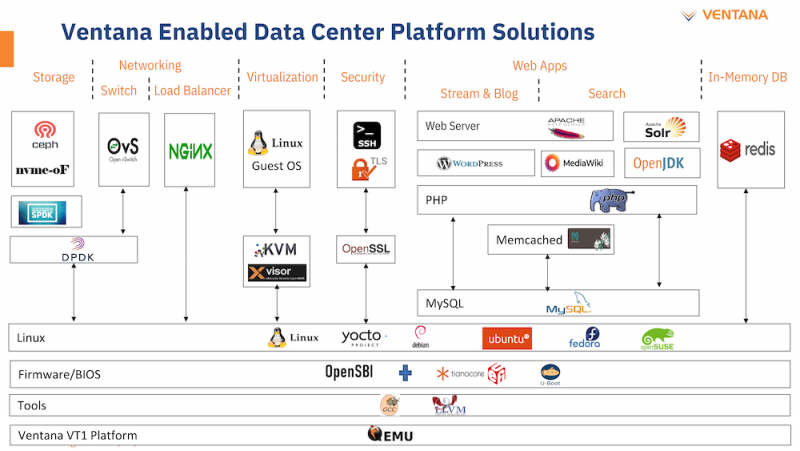

Auch den Software-Support hat das Unternehmen nicht vergessen: Die Ventana Veyron V1-Entwicklerplattformen werden von einem vollwertigen SDK begleitet, bei dem die Hauptsoftware bereits auf die neue Architektur portiert ist. Die Liste umfasst die GCC- und LLVM-Compiler, den OpenOCD/GDB-Debugger, U-Boot und Tianocore UEFI EDK2.1-Loader-Quellen und -Binärdateien. Eine Reihe von Linux-Distributionen sowie andere System- und Anwendungssoftware werden unterstützt. Die neuen Systeme sollen Anfang nächsten Jahres verfügbar sein.

2022-12-14 08:08:37

Autor: Vitalii Babkin

Quell-URL