Im Rahmen des Architecture Day sprach Intel über die kommenden Sapphire Rapids Serverprozessoren, bestätigte die meisten der zuvor veröffentlichten Informationen und ergänzte sie um einige Details. Intel positioniert neue Produkte als Lösung für eine breitere Palette von Aufgaben und Workloads als zuvor, einschließlich der mittlerweile beliebten Microservices, Containerisierung und Virtualisierung. Das Unternehmen verspricht, dass CPUs in Bezug auf Rechenleistung, Speicher und I/O ausgewogen sein werden.

Die neuen Prozessoren erhielten endlich ein Chiplet- oder Tile-Layout in der Intel-Terminologie - der SoC enthält vier "Core"-Kacheln, die auf der Intel 7-Prozesstechnologie (10 nm Enhanced SuperFIN) basieren. Jede Kachel ist über EMIB mit ihrem Nachbarn verbunden. Ihre Systemagenten, einschließlich bis zu 100+ MB des gesamten L3-Cache, bilden ein schnelles Mesh-Netzwerk mit einer Latenz von etwa 4-8 ns in eine Richtung. Von außen „scheint“ der Prozessor monolithisch zu sein.

Jeder Kern oder Thread hat freien Zugriff auf alle Ressourcen benachbarter Kacheln, einschließlich Cache, Speicher, Beschleuniger und IO-Blöcke. Potenziell ist dieser Ansatz aus Sicht des internen Datenaustauschs profitabler als im Fall von AMD mit einer gemeinsamen IO-Einheit für alle Chiplets, die in zukünftigen EPYCs bereits 12 sein werden. Aber wie es tatsächlich wird, werden wir wissen erst nächstes Jahr - die Veröffentlichung von Sapphire Rapids ist für das erste Quartal 2022 geplant, die Massenproduktion im zweiten Quartal.

Sapphire Rapids basieren auf der Golden Cove-Mikroarchitektur, die breiter, tiefer und intelligenter ist. Es soll auch in hochleistungsfähigen Alder-Lake-Kernen zum Einsatz kommen, bei Server-Prozessoren gibt es jedoch einige Unterschiede. Beispielsweise wurde der L2-Cache auf 2 MB pro Kern erhöht oder der neue AMX-Befehlssatz (Advanced Matrix Extension). Letzteres erweitert die KI-Funktionalität der CPU und ermöglicht MAC-Operationen auf Matrizen, die für diese Art von Workload typisch sind.

Für AMX gibt es acht dedizierte 2D-Register mit einem Volumen von jeweils 1 KB (sechzehn 64-Byte-Zeilen). Eine separate Hardwareeinheit führt MAC-Operationen an drei Registern durch, und dies kann parallel zur Ausführung anderer Befehle im Rest des Kernels erfolgen. Das Einstellen der Parameter und Inhalte der Register sowie das Verschieben von Daten wird von der OS übernommen. Bisher wird in den Prozessoren nur der MAC-Block präsentiert, aber in Zukunft können Blöcke für andere, komplexere Operationen erscheinen.

In der Spitze beträgt die AMX-Leistung auf INT8 2048 Operationen pro Zyklus pro Kern, was achtmal schneller ist als bei herkömmlichen AVX-512-Befehlen (an zwei FMA-Ports). Beim BF16 ist die AMX-Leistung doppelt so niedrig, aber das ist immer noch eine deutliche Steigerung im Vergleich zur vorherigen Xeon-Generation - Intel versucht immer noch, universelle Kerne zu schaffen, die nicht nur mit Inferenz, sondern auch mit dem Training von KI-Modellen zurechtkommen. Das Unternehmen sagt jedoch, dass die CPU-Fähigkeiten von AMX die GPUs ergänzen, anstatt direkt mit ihnen zu konkurrieren.

Es ist Sapphire Rapids, die den BF16 endlich weiter verbreiten sollte, da Cooper Lake, wo die Unterstützung dieses Datenformats erstmals in Intel-CPUs auftauchte, eine eher enge Anwendungsnische hat. Weitere Architektur-Updates umfassen FP16-Unterstützung für AVX-512, Anweisungen für schnelles Hinzufügen (FADD) und effizienteres Datenmanagement in der Cache-Hierarchie (CLDEMOTE), eine Reihe neuer Anweisungen und Interrupts für die Arbeit mit Speicher und TLBs für virtuelle Maschinen (VM) , erweiterte Telemetrie mit Mikrosekundenzählung und so weiter.

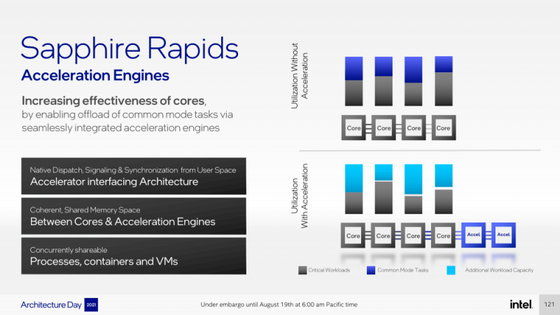

Die letzten Punkte werden im Allgemeinen für ein effizienteres und intelligenteres Ressourcenmanagement und QoS für Prozesse, Container und VMs benötigt – sie alle reduzieren irgendwie die Overhead-Kosten. Dedizierte Beschleuniger beschleunigen die Arbeit noch mehr. Bisher wurden nur zwei erwähnt. Der erste, DSA (Data Streaming Accelerator), beschleunigt die Bewegung und Übertragung von Daten sowohl innerhalb eines einzelnen Hosts als auch zwischen mehreren Hosts. Dies ist nützlich, wenn es um Arbeitsspeicher, Speicher, Netzwerkverkehr und Virtualisierung geht.

Der zweite erwähnte Beschleuniger ist die QAT (Quick Assist Engine), die für Operationen oder gleichzeitig eine Operationskette (De-)Komprimierung (bis zu 160 Gbps in beide Richtungen gleichzeitig), Hashing und Verschlüsselung (up bis 400 Gbit/s) in gängigen Algorithmen: AES GCM / XTS, ChaChaPoly, DH, ECC usw. Jetzt ist der QAT-Block Teil des Prozessors selbst geworden, während er zuvor als Teil einiger Chipsätze oder als separate Erweiterungskarte erhältlich war. Dadurch konnten Verzögerungen reduziert und die Blockleistung erhöht werden.

Darüber hinaus kann QAT beispielsweise für die Virtualisierung oder die Intel Accelerator Interfacing Architecture (AiA) verwendet werden. AiA ist ein weiterer neuer Befehlssatz, der entwickelt wurde, um mit integrierten und diskreten Beschleunigern effizienter zu arbeiten. AiA hilft bei der Steuerung, dem Timing und der Signalisierung, was wiederum einen Teil des Overheads bei der Interaktion mit User-Space-Beschleunigern reduziert.

Das Speichersubsystem umfasst vier Dual-Channel-DDR5-Controller, einen für jede Kachel. Voraussichtlich wird es vier verfügbare NUMA-Domains geben. Abgesehen von der erwähnten Unterstützung für das Intel Optane PMem 300 der nächsten Generation (Crow Pass) wurden keine weiteren Details genannt. Aber das Vorhandensein von Modellen mit onboard HBM wurde offiziell bestätigt, auch ein Modul pro Kachel. HBM kann als DRAM-Cache oder unabhängig verwendet werden. In einigen Fällen wird es möglich sein, ganz auf DRAM zu verzichten.

Zu PCIe 5.0 und CXL 1.1 (CXL.io, CXL.cache, CXL.memory) gibt es nichts hinzuzufügen, obwohl Intel in einem anderen Bericht klarstellte, dass man auf CXL als Interconnect nicht nur innerhalb eines Knotens, sondern auch in die Zukunft auf Rack-Ebene. Um die CPU (nahtlos bis 8S) zu kombinieren, wird weiterhin der UPI-Bus verwendet, jedoch bereits der zweiten Generation (16 GT/s pro Leitung) - 24 Leitungen pro Kachel.

Speziell für Sapphire Rapids liefert Intel noch keine genauen Daten zum Wachstum von IPC im Vergleich zu Ice Lake-SP und beschränkt sich in einigen Aufgaben und Bereichen nur auf einzelne Zahlen. Eine Reihe weiterer wichtiger Parameter wurde ebenfalls nicht angegeben. Allerdings liegt AMD EPYC Genoa laut den neuesten Leaks auch in rein quantitativen Eigenschaften deutlich vor Sapphire Rapids.

2021-08-19 15:22:46

Autor: Vitalii Babkin