Dans le cadre de l'Architecture Day, Intel a parlé des prochains processeurs de serveur Sapphire Rapids, confirmant la plupart des informations précédemment publiées et les complétant par quelques détails. Intel positionne les nouveaux produits comme une solution pour un plus large éventail de tâches et de charges de travail qu'auparavant, y compris les microservices, la conteneurisation et la virtualisation désormais populaires. La société promet que les CPU seront équilibrés en termes de calcul, de mémoire et d'E/S.

Les nouveaux processeurs ont finalement obtenu une disposition de puces, ou tuile dans la terminologie Intel, - le SoC comprend quatre tuiles "noyaux" basées sur la technologie de processus Intel 7 (10 nm Enhanced SuperFIN). Chaque tuile est connectée à sa voisine via EMIB. Leurs agents système, comprenant jusqu'à 100+ Mo de cache L3 total, forment un réseau maillé rapide avec une latence d'environ 4 à 8 ns dans une direction. De l'extérieur, le processeur « semblera » être monolithique.

Chaque cœur ou thread aura un accès gratuit à toutes les ressources des tuiles voisines, y compris le cache, la mémoire, les accélérateurs et les blocs d'E/S. Potentiellement, cette approche est plus rentable du point de vue de l'échange de données interne que dans le cas d'AMD avec une unité d'E/S commune pour toutes les puces, qui à l'avenir les EPYC seront déjà 12. Mais comment ce sera réellement, nous le saurons seulement l'année prochaine - la sortie de Sapphire Rapids est prévue pour le premier trimestre 2022, avec une production de masse au deuxième trimestre.

Sapphire Rapids est basé sur la microarchitecture Golden Cove, qui est plus large, plus profonde et plus intelligente. Il sera également utilisé dans les cœurs hautes performances d'Alder Lake, mais il existe quelques différences dans le cas des processeurs de serveur. Par exemple, le cache L2 est passé à 2 Mo par cœur ou le nouveau jeu d'instructions AMX (Advanced Matrix Extension). Ce dernier étend la fonctionnalité AI du CPU et permet des opérations MAC sur des matrices, ce qui est typique pour ce type de charge de travail.

Pour AMX, il existe huit registres 2D dédiés d'un volume de 1 Ko chacun (seize lignes de 64 octets). Une unité matérielle distincte effectue des opérations MAC sur trois registres, et cela peut être fait en parallèle avec l'exécution d'autres instructions dans le reste du noyau. Le réglage des paramètres et du contenu des registres, ainsi que le mouvement des données sont gérés par le système d'exploitation. Jusqu'à présent, seul le bloc MAC est présenté dans les processeurs, mais des blocs pour d'autres opérations plus complexes peuvent apparaître à l'avenir.

À son apogée, les performances AMX sur INT8 sont de 2048 opérations par cycle et par cœur, ce qui est huit fois plus rapide que les instructions AVX-512 traditionnelles (sur deux ports FMA). Sur le BF16, les performances AMX sont deux fois plus faibles, mais il s'agit toujours d'une augmentation significative par rapport à la génération précédente Xeon - Intel essaie toujours de créer des cœurs universels capables de gérer non seulement l'inférence, mais également la formation de modèles d'IA. Cependant, la société affirme que les capacités CPU d'AMX compléteront les GPU plutôt que de rivaliser directement avec eux.

C'est Sapphire Rapids qui devrait enfin généraliser le BF16, puisque Cooper Lake, où le support de ce format de données est apparu pour la première fois dans les processeurs Intel, a un créneau d'application assez étroit. Les autres mises à jour architecturales incluent la prise en charge de FP16 pour AVX-512, les instructions pour l'ajout rapide (FADD) et une gestion plus efficace des données dans la hiérarchie du cache (CLDEMOTE), un certain nombre de nouvelles instructions et interruptions pour travailler avec la mémoire et les TLB pour les machines virtuelles (VM) , télémétrie avancée avec comptage de microsecondes, et ainsi de suite.

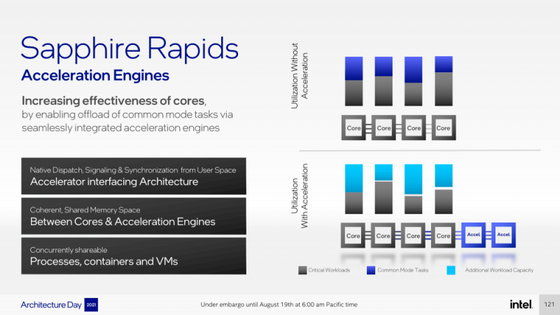

Les derniers points, en général, sont nécessaires pour une gestion des ressources et une qualité de service plus efficaces et intelligentes pour les processus, les conteneurs et les machines virtuelles - tous réduisent d'une manière ou d'une autre les frais généraux. Des accélérateurs dédiés accélèrent encore plus le travail. Jusqu'à présent, seuls deux ont été mentionnés. Le premier, DSA (Data Streaming Accelerator), accélère le mouvement et le transfert de données à la fois au sein d'un seul hôte et entre plusieurs hôtes. Ceci est utile pour gérer la mémoire, le stockage, le trafic réseau et la virtualisation.

Le deuxième accélérateur évoqué est le QAT (Quick Assist Engine), qui peut être utilisé pour des opérations ou à la fois une chaîne d'opérations (dé-)compression (jusqu'à 160 Gbps dans les deux sens en même temps), hachage et chiffrement (jusqu'à à 400 Gbps) dans les algorithmes populaires : AES GCM/XTS, ChaChaPoly, DH, ECC, etc. Désormais, le bloc QAT fait désormais partie du processeur lui-même, alors qu'auparavant il était disponible dans le cadre de certains chipsets ou en tant que carte d'extension séparée. Cela a permis de réduire les délais et d'augmenter les performances des blocs.

De plus, QAT peut être utilisé, par exemple, pour la virtualisation ou Intel Accelerator Interfacing Architecture (AiA). AiA est un autre nouveau jeu d'instructions conçu pour fonctionner plus efficacement avec des accélérateurs intégrés et discrets. AiA aide au contrôle, à la synchronisation et à la signalisation, ce qui, encore une fois, réduira une partie des frais généraux lors de l'interaction avec les accélérateurs de l'espace utilisateur.

Le sous-système de mémoire comprend quatre contrôleurs DDR5 double canal, un pour chaque tuile. Vraisemblablement, il y aura quatre domaines NUMA disponibles. Outre la prise en charge mentionnée pour la prochaine génération d'Intel Optane PMem 300 (Crow Pass), plus de détails n'ont pas été fournis. Mais la présence de modèles avec HBM embarqué a été officiellement confirmée, également un module par tuile. HBM peut être utilisé comme cache DRAM ou indépendamment. Dans certains cas, il sera possible de se passer de DRAM du tout.

Il n'y a rien à ajouter à propos de PCIe 5.0 et CXL 1.1 (CXL.io, CXL.cache, CXL.memory), bien que dans un autre rapport, Intel ait clairement indiqué qu'il s'appuie sur CXL comme interconnexion non seulement au sein d'un nœud, mais également dans l'avenir au niveau du rack. Pour combiner le CPU (en toute transparence jusqu'à 8S), le bus UPI sera toujours utilisé, mais déjà de deuxième génération (16 GT/s par ligne) - 24 lignes par tuile.

Spécifiquement pour Sapphire Rapids, Intel n'a pas encore fourni de données précises sur la croissance de l'IPC par rapport à Ice Lake-SP, se limitant uniquement à des chiffres individuels dans certaines tâches et certains domaines. Un certain nombre d'autres paramètres importants n'ont pas non plus été spécifiés. Cependant, AMD EPYC Genoa, selon les dernières fuites, est nettement en avance sur Sapphire Rapids, même en termes de caractéristiques purement quantitatives.

2021-08-19 15:22:46

Auteur: Vitalii Babkin