Finanzinstitute, Reservierungssysteme und andere geschäftskritische Betreiber schätzen die "großen Maschinen" von IBM wegen ihrer Zuverlässigkeit. Kein Wunder, dass der Buchstabe z im Namen der Systeme Zero Downtime – Zero Downtime bedeutet. Auf der Konferenz Hot Chips 33 stellte das Unternehmen eine neue Generation von Z-Prozessoren vor, die erstmals in der Geschichte den eigenen Namen Telum (dart in Latein) erhielten. Der Name "Waffe" wurde aus einem bestimmten Grund gewählt: In der neuen Architektur führte IBM auch neue Lösungen ein, die bisher in System z nicht verwendet wurden, insbesondere zur Betrugsbekämpfung.

Einige der wichtigsten Kunden von IBM – große Finanzkonzerne und Banken – warten schon lange auf eingebaute KI-Tools, da ihre Systeme Tausende und Abertausende von Transaktionen pro Sekunde verarbeiten müssen, und dies so zuverlässig wie möglich. Eines der Ziele bei der Entwicklung von Telum war die Einführung von Inferenzberechnungen, die in Echtzeit direkt während der Verarbeitung einer Transaktion erfolgen und ohne dass Daten außerhalb des Systems gesendet werden.

Daher ist der Inferenzbeschleuniger in Telum direkt mit dem Cache-Subsystem verbunden und nutzt alle z/Architecture-Prozessor- und Speicherschutzmechanismen. Und er selbst trägt auch eine Reihe von Ansätzen, die für z. So steuert eine separate „Firmware“ den Betrieb des Beschleunigers, die verändert werden kann, um die Aufgaben eines bestimmten Clients zu optimieren. Es wird auf einem der Kerne und dem Beschleuniger selbst ausgeführt, der mit diesem Kern kommuniziert und für den Zugriff auf Speicher und Cache, Sicherheit und Datenintegrität sowie die Verwaltung der eigentlichen Berechnungen verantwortlich ist.

Der Beschleuniger umfasst zwei Arten von Motoren. Der erste hat 128 SIMD-Blöcke für MAC-Operationen mit FP16-Daten und wird für Matrixmultiplikation und Faltung benötigt. Der zweite hat nur 32 SIMD-Blöcke, kann aber mit FP16 / FP32-Daten arbeiten und ist für Netzwerkaktivierungsfunktionen und andere komplexere Aufgaben optimiert. Ergänzt werden sie durch einen Block ultraschnellen Speichers (Scratchpad) und eine "intelligente" IO-Engine, die für das Verschieben und Vorbereiten von Daten verantwortlich ist und diese im Handumdrehen neu formatieren kann.

Scratchpad ist mit einem Block verbunden, der Daten aus dem L2-Cache herunterlädt und die Ergebnisse der Berechnungen zurücksendet. IBM betont separat, dass das Vorhandensein eines dedizierten KI-Beschleunigers die parallele Verwendung herkömmlicher SIMD-Blöcke in den Kernen ermöglicht, was eindeutig auf das AVX-512-VNNI hindeutet. Allerdings haben Sapphire Rapids nun auch eine eigene AMX-Einheit im Kern, die allerdings in der Funktionalität bescheidener ausfällt.

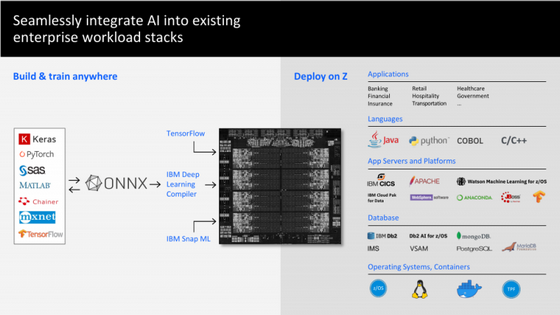

Auf den Beschleuniger kann vom Benutzerbereich aus zugegriffen werden, auch in einer virtualisierten Umgebung. Um mit dem neuen Accelerator zu arbeiten, bietet das Unternehmen den IBM Deep Learning Compiler an, der importierte ONNX-Modelle optimieren soll. Es gibt auch sofort einsatzbereite Unterstützung für TensorFlow, IBM Snap ML und eine Reihe beliebter Entwicklungstools. Es gibt einen KI-Beschleuniger pro Prozessor mit einer Leistung von mehr als 6 Teraflops FP16.

Beim Test-RNN-Modell zum Schutz vor Betrug kann der Chip 116 Tausend Inferenzoperationen mit einer Latenzzeit von 1,1 ms ausführen, bei einem System mit 32 Prozessoren sind es bereits 3,6 Millionen Inferenzoperationen, und die Latenzzeit steigt 1,2 ms. Neben dem KI-Beschleuniger gibt es auch einen für alle Kerne gemeinsamen (De-)Kompressions-(gzip)-Beschleuniger + jeder Kern besitzt auch eine Engine für CSMP. Nun, Beschleuniger für Sortierung und Verschlüsselung sind auch nirgendwo hingegangen.

Für die Zuverlässigkeit sind Hunderte verschiedener Mechanismen zur Überprüfung und Nachprüfung der Funktionsfähigkeit verantwortlich. So werden zum Beispiel die Register und der Cache dupliziert, um bei einem Ausfall des yal einen vollständigen Neustart zu ermöglichen und die Ausführung von Aufgaben genau an der Stelle fortzusetzen, an der sie unterbrochen wurde. Und für den unbedingt verschlüsselten Arbeitsspeicher kommt der Redundant Array of Memory (RAIM)-Modus zum Einsatz, eine Art RAID-Array, bei dem eine Cache-Zeile zwischen acht Modulen gleichzeitig "verschmiert" wird.

Telum, das viel von seinem Vorgänger z15 erbt, unterscheidet sich noch radikal davon. Der Prozessor enthält acht Kerne mit Unterstützung für "intelligente" Deep-Out-of-Order-Execution und SMT2 mit einer Frequenz von über 5 GHz. Jeder Kern ist auf 32 MB L2-Cache angewiesen, sodass andere moderne CPUs vor ihrem Hintergrund langweilig aussehen. Aber es ist nicht so einfach.

Die Caches kommunizieren untereinander über einen bidirektionalen Ringbus mit einer Bandbreite von mehr als 320 GB/s und bilden somit einen virtuellen L3-Cache mit einem Volumen von 256 MB und mit einer durchschnittlichen Latenz von 12 ns. Jeder Telum-Chip kann einen (SCM) oder zwei (DCM) Prozessoren enthalten. Und in einem Knoten können sich bis zu vier Chips befinden, also bis zu acht CPUs, die nach dem Schema jeweils mit der gleichen Geschwindigkeit von 320 GB / s kombiniert werden.

Somit wird im Rahmen des Knotens ein virtueller L4-Cache mit einem Volumen von 2 GB gebildet. Die flache Topologie der Caches sorgt laut IBM für neue Prozessoren mit geringerer Latenz im Vergleich zum z15. Eine Skalierung auf bis zu 32 Prozessoren ist möglich, einzelne Knoten werden jedoch durch Mehrfachverbindungen mit „nur“ 45 GB/s pro Weg verbunden.

IBM meldet eine Leistungssteigerung von 40 % gegenüber dem z15 pro Sockel. Telum enthält 22 Milliarden Transistoren und hat im Normalmodus eine TDP von 400 W.

2021-08-24 04:55:13

Autor: Vitalii Babkin