金融機関、予約システム、およびその他のビジネスクリティカルなオペレーターは、その信頼性のためにIBMの「ビッグマシン」を愛しています。システム名の文字zがゼロダウンタイム(ゼロダウンタイム)を意味するのも不思議ではありません。 Hot Chips 33カンファレンスで、同社は新世代のzプロセッサを発表しました。これは、歴史上初めて独自の名前であるTelum(ラテン語でダーツ)を取得しました。 「武器」の名前が選ばれた理由は次のとおりです。新しいアーキテクチャーでは、IBMは、特に詐欺と戦うために設計された、以前はSystemzで使用されていなかった新しいソリューションも導入しました。

IBMの主要な顧客の一部(大規模な金融会社や銀行)は、システムが1秒あたり数千、数千のトランザクションを処理し、可能な限り確実に処理する必要があるため、組み込みのAIツールを長い間待っていました。 Telumの開発における目標の1つは、トランザクションの処理中にリアルタイムで、システムの外部にデータを送信せずに発生する推論計算を導入することでした。

したがって、Telumの推論アクセラレータはキャッシュサブシステムに直接接続され、すべてのz / Architectureプロセッサとメモリ保護メカニズムを使用します。そして彼自身もzに特徴的な多くのアプローチを持っています。したがって、別の「ファームウェア」がアクセラレータの動作を制御します。アクセラレータは、特定のクライアントのタスクを最適化するために変更できます。コアの1つと、このコアと通信するアクセラレータ自体で実行され、メモリとキャッシュへのアクセス、セキュリティとデータの整合性、および実際の計算の管理を担当します。

アクセルには2種類のエンジンがあります。 1つ目はFP16データを使用したMAC操作用の128個のSIMDブロックを持ち、行列の乗算と畳み込みに必要です。 2つ目は32個のSIMDブロックしかありませんが、FP16 / FP32データで動作し、ネットワークアクティベーション機能やその他のより複雑なタスク用に最適化されています。これらは、超高速メモリのブロック(スクラッチパッド)と、データの移動と準備を担当する「スマート」IOエンジンによって補完され、データをオンザフライで再フォーマットできます。

スクラッチパッドは、L2キャッシュからデータをダウンロードし、計算結果を送り返すブロックに接続されています。 IBMは、専用のAIアクセラレーターの存在により、コアで従来のSIMDブロックを並行して使用できることを個別に強調し、AVX-512VNNIを明確に示唆しています。ただし、Sapphire Rapidsのコアには別のAMXユニットもありますが、機能はそれほど控えめです。

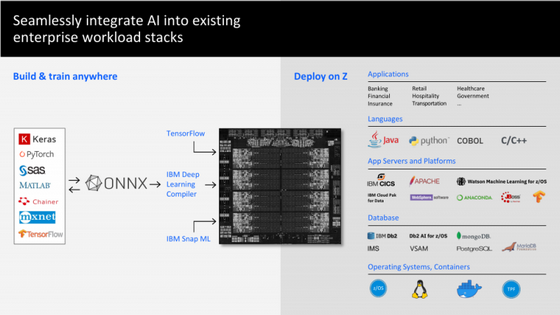

アクセラレータには、仮想化環境を含め、ユーザースペースからアクセスできます。新しいアクセラレーターを使用するために、同社はインポートされたONNXモデルの最適化に役立つIBM Deep LearningCompilerを提供しています。 TensorFlow、IBM Snap ML、およびさまざまな一般的な開発ツールもすぐにサポートされます。プロセッサごとに1つのAIアクセラレータがあり、6テラフロップス以上のFP16のパフォーマンスを発揮します。

不正からの保護のためのテストRNNモデルでは、チップは1.1ミリ秒以内の遅延で116千の推論操作を実行でき、32プロセッサのシステムの場合、この数字はすでに360万の推論操作であり、遅延はわずかに増加します。 1.2ミリ秒。 AIアクセラレータに加えて、すべてのコアに共通の(de-)圧縮(gzip)アクセラレータもあります+各コアにはCSMP用のエンジンもあります。さて、ソートと暗号化のためのアクセラレータもどこにも行きませんでした。

操作性をチェックおよび再チェックするための何百もの異なるメカニズムが信頼性に責任があります。そのため、たとえば、レジスタとキャッシュが複製され、yalに障害が発生した場合に、yalを完全に再起動して、中断された場所から正確にタスクの実行を続行できます。また、必然的に暗号化されるRAMには、RAIDアレイの一種である冗長メモリアレイ(RAIM)モードが使用されます。このモードでは、1つのキャッシュラインが8つのモジュール間で一度に「スミア」されます。

Telumは、その前身であるz15から多くを継承していますが、それでも根本的に異なります。プロセッサには、5GHzを超える周波数で動作する「スマート」なディープアウトオブオーダー実行とSMT2をサポートする8つのコアが含まれています。各コアは32MBのL2キャッシュに依存しているため、他の最新のCPUはそのバックグラウンドに対して鈍く見えます。しかし、それはそれほど単純ではありません。

キャッシュは、320 GB / sを超える帯域幅の双方向リングバスを介して相互に通信するため、ボリュームが256 MB、平均遅延が12nsの仮想L3キャッシュを形成します。各Telumチップには、1つ(SCM)または2つ(DCM)のプロセッサを含めることができます。また、1つのノードには、最大4つのチップ、つまり最大8つのCPUを、それぞれのスキームに従って組み合わせることができます。それぞれの速度は、320 GB / sです。

したがって、ノードのフレームワーク内で、2GBのボリュームを持つ仮想L4キャッシュが形成されます。 IBMによると、キャッシュのフラット・トポロジーは、z15と比較してより低いレイテンシーで新しいプロセッサーを提供します。最大32プロセッサのスケーリングが可能ですが、個々のノードは、片道「わずか」45GB /秒で複数の接続によってリンクされます。

IBMは、ソケットあたりz15よりもパフォーマンスが40%向上したと報告しています。 Telumには220億個のトランジスタが含まれており、通常モードでのTDPは400Wです。

2021-08-24 04:55:13

著者: Vitalii Babkin