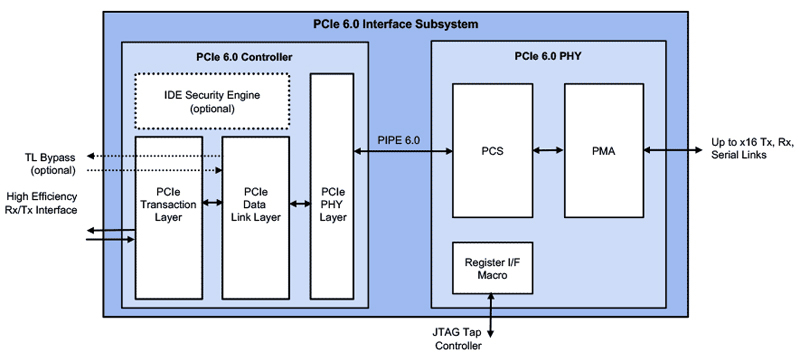

Rambus kündigte die Verfügbarkeit seiner PCI Express (PCIe) 6.0-Lösungen an, die sowohl auf Server-SoCs als auch auf KI-Chips abzielen. Die angekündigte Lösung umfasst einen PHY-Chip und einen Controller. Die Rambus PCIe 6.0-Schnittstelle soll vollständig optimiert sein, um die Anforderungen heterogener Computerarchitekturen zu erfüllen. Erwähnt werden die Unterstützung für CXL 3.0 und die Abwärtskompatibilität mit PCIe 5.0, 4.0 und 3.0/3.1.

Der Rambus PCIe 6.0-Controller enthält eine IDE-Engine (Integrity and Data Encryption), die PCIe-Lanes überwacht und vor physischen Angriffen schützt. Implementierung verschiedener Mechanismen zur Verbesserung der Effizienz der Schnittstelle und der FEC-Fehlerkorrekturtechnologie. Die vollständige Unterstützung für CXL 3.0 auf der PHY-Seite bietet verbesserte Speicherpooling-Funktionen, erweiterte Kohärenzmodi und Multilayer-Switching.

„Die rasante Entwicklung von KI, maschinellem Lernen und datenintensiven Workloads treibt die kontinuierliche Weiterentwicklung von Rechenzentrumsarchitekturen voran, die eine immer höhere Leistung erfordern. Das Rambus PCIe 6.0-Subsystem ist in der Lage, die Anforderungen von Rechenzentren der nächsten Generation in Bezug auf Latenz, Leistung, Platzbedarf und Sicherheit zu erfüllen“, sagt Rambus.

2022-10-26 14:10:11

Autor: Vitalii Babkin