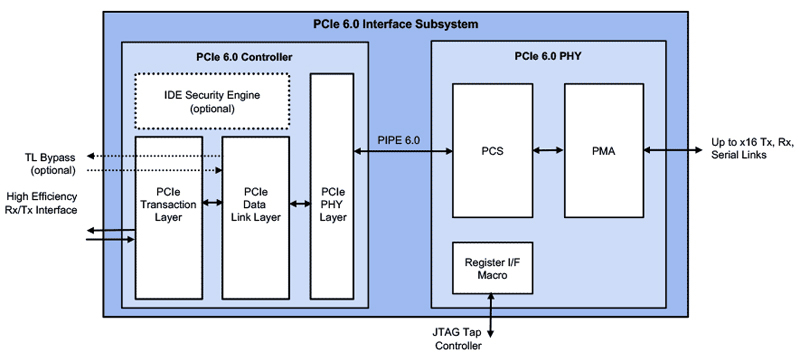

Rambus a annoncé la disponibilité de ses solutions PCI Express (PCIe) 6.0, qui ciblent les SoC des serveurs ainsi que les puces AI. La solution annoncée comprend une puce PHY et un contrôleur. L'interface Rambus PCIe 6.0 serait entièrement optimisée pour répondre aux besoins des architectures informatiques hétérogènes. La prise en charge de CXL 3.0 et la rétrocompatibilité avec PCIe 5.0, 4.0 et 3.0/3.1 sont mentionnées.

Le contrôleur Rambus PCIe 6.0 contient un moteur IDE (Integrity and Data Encryption) qui surveille et protège les voies PCIe contre les attaques physiques. Mise en œuvre de divers mécanismes pour améliorer l'efficacité de l'interface et de la technologie de correction d'erreurs FEC. La prise en charge complète de CXL 3.0 côté PHY offre des capacités améliorées de mise en commun de la mémoire, des modes de cohérence avancés et une commutation multicouche.

« L'évolution rapide de l'IA, de l'apprentissage automatique et des charges de travail gourmandes en données entraîne l'évolution continue des architectures de centres de données qui nécessitent des performances toujours plus élevées. Le sous-système Rambus PCIe 6.0 est capable de répondre aux besoins des centres de données de nouvelle génération en termes de latence, de puissance, d'encombrement et de sécurité », déclare Rambus.

2022-10-26 14:10:11

Auteur: Vitalii Babkin