今週、Western Digitalは、今後数年間の3DNANDメモリ開発計画を発表しました。とりわけ、同社は、パートナーの日本企業であるキオクシアと共同で、セル面積を削減した162層フラッシュメモリチップと200層以上の高性能フラッシュメモリを開発していると述べました。

次世代の3DNANDメモリBiCS6は、今年の終わりに登場します。一見すると、これらは垂直層の数の点で最も先進的なチップではなく、わずか162層であり、Micronによって導入されたばかりの232層の3DNANDチップの背景に対してかなり控えめに見えます。ただし、WDソリューションとMicronソリューションの容量は同じで、128 GB(1 Tbit)です。そして、BiCS6の面積は業界で最もコンパクトな68mm2になります。同社は、メモリセルの物理的なサイズを大幅に縮小することでこれを達成することができました。これは、メモリセルの構造に新しい材料を使用することで実現しました。

さらに、BiCS6メモリは各セル(QLC)に4ビットを格納します。それぞれに4ビットを書き込むことを組み合わせてセルの物理サイズを小さくすると、書き換えサイクル数が減るはずですが、WDはまだこの値を開示していません。同時に、BiCS6メモリの速度は最新のソリューションの場合よりも60%速くなることが約束されており、マスドライブと大容量サーバーSSDの両方の生産に使用できるようになります。密度を上げると、生産コストも削減されます。これは誰にとっても重要です。

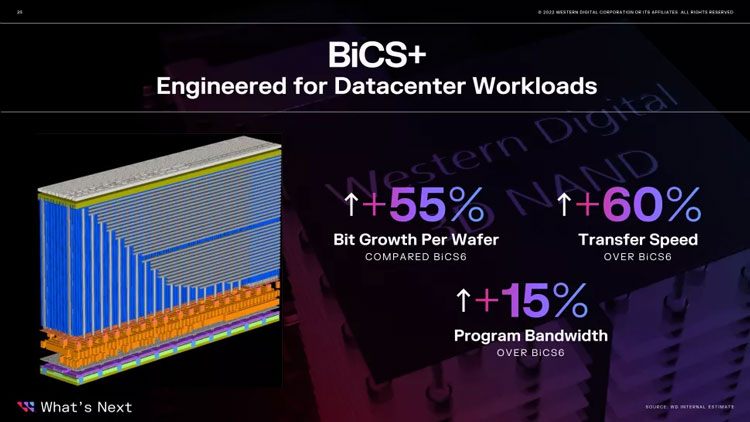

もう1つの新しい開発は、それほど興味深いものではありません。BiCS+200層を超えるメモリです。主にサーバーサイドSSD向けにゼロから開発されていると言われています。 BiCS +メモリは2024年までに登場し、BiCS6メモリと比較してプラッタあたりのビット数が最大55%増加し、速度が最大60%向上します。また、書き込み速度は15%向上します。これは、NANDフラッシュメモリにとって他のすべてよりも重要です。

今後、WDは他の3D NANDベンダーと同様に、500以上の3DNANDレイヤーを目指しています。このようなメモリは、メモリ結晶の垂直方向の「接着」を含む多くの技術の組み合わせを使用してのみ生成できます。同社は、セルあたり5ビット(PLC)のメモリをリリースするという希望を失うことはありませんが、500層の3D NANDをリリースするのと同じくらい難しく、登場時間が遅れます。

2022-05-13 10:19:30

著者: Vitalii Babkin