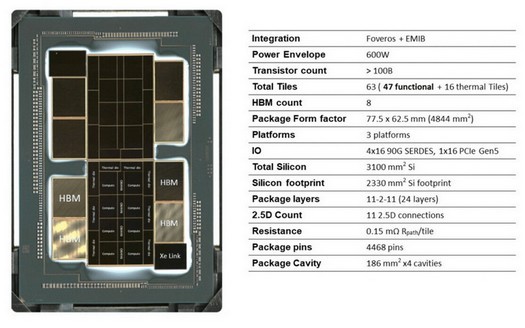

国際固体回路会議(ISSCC)2022で、インテルは、今後のポンテヴェッキオサーバーコンピューティングアクセラレーターに関する最新の詳細を共有しました。これに先立ち、メーカーは、ヴェッキオ橋が1つの基板上で組み合わされた47個の個別の要素(Intelではタイル)を使用することを繰り返し述べてきました。実際、アクセラレータには合計63個のタイルがありますが、機能しているのは47個だけです。

ヴェッキオ橋には、16タイルのコンピューティングユニットと8つのRAMBOキャッシュクリスタルを収容する2つのベースクリスタルが含まれています。近くには、8つのHBM2EメモリスタックとXeLinkバスクリスタルがあります。 EMIBバスは、合計11個の水晶を使用して、アクセラレータ内のすべてのチップ間の接続を担当します。パッケージングには、独自技術のIntelFoverosが使用されます。また、Ponte Vecchioアクセラレータには、アクティブチップからの熱をより均一に分散させる16個の「サーモプレート」が含まれています。

Intelは、RAMBOキャッシュに関する詳細も共有しました。各チップには、それぞれ3.75MBの容量を持つ4つのSRAMメモリブロックが含まれています。したがって、1つのタイルのRAMBOキャッシュの量は15MBです。つまり、8つのRAMBOキャッシュタイルにより、アクセラレータに合計120MBの追加キャッシュが提供されます。このキャッシュの各タイルは、1.3TB / sのバスで接続されています。比較すると、ヴェッキオ橋の計算タイルは、2.6 TB / sのバスでベースタイルと組み合わされています。

ベースダイについては、L3キャッシュ(144 MB)、8つのHBMメモリコントローラー、16レーンのPCIe 5.0コントローラーまたはCXL、電圧コントローラー(完全統合電圧レギュレーター、FIVR)などのさまざまなコントローラーとバスが含まれています。コントロール。 Intel 7(10 nm)プロセステクノロジーを使用して生成される1つのベースタイルの面積は646mm2です。 17層で構成されています。

ヴェッキオ橋のコンピューティングブロックは、TSMCの5nmプロセス技術を使用して作られています。後者はまた、Xe-Linkコントローラーで7nmテクノロジーを使用してタイルを生成します。 Intelは、Intel 7(10nm)テクノロジを使用して、独自のRAMBOキャッシュとFoverosパッケージのベースタイルを製造しています。空冷を使用する場合、ヴェッキオ橋の最大TDPは450ワットと記載されています。ただし、液体冷却を使用する場合、この数値は600ワットに達します。記載されている動作温度範囲は65〜81°Cです。

47個のアクティブなタイルの総面積は2330mm2です。 16枚のサーマルタイルと合わせて、3100mm2に増加します。同時に、4468接点を使用してシステムに接続されている、パッケージ内のポンテヴェッキオアクセル全体の総面積は4844mm2です。トランジスタの総数は1000億を超えています。

2022-02-22 16:07:25

著者: Vitalii Babkin