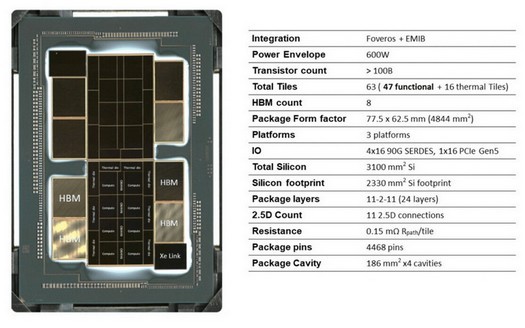

Lors de la Conférence internationale sur les circuits à semi-conducteurs (ISSCC) 2022, Intel a partagé de nouveaux détails sur ses prochains accélérateurs informatiques pour serveurs Ponte Vecchio. Avant cela, le fabricant a déclaré à plusieurs reprises que le Ponte Vecchio utilisera 47 éléments distincts (tuiles en termes d'Intel), combinés sur un seul substrat. En fait, l'accélérateur compte 63 tuiles au total, mais seulement 47 d'entre elles sont fonctionnelles.

Le Ponte Vecchio contient deux cristaux de base, qui abritent seize tuiles d'unités de calcul et huit cristaux de cache RAMBO. A proximité se trouvent huit piles de mémoire HBM2E et des cristaux de bus Xe Link. Le bus EMIB est responsable de la connexion entre toutes les puces des accélérateurs, avec un total de 11 cristaux. Pour l'emballage, la technologie propriétaire Intel Foveros est utilisée. De plus, les accélérateurs Ponte Vecchio contiennent 16 "thermoplaques" responsables d'une répartition plus uniforme de la chaleur des puces actives.

Intel a également partagé des détails sur le cache RAMBO. Chaque puce comprend quatre blocs de mémoire SRAM, chacun d'une capacité de 3,75 Mo. Ainsi, la quantité de cache RAMBO dans une tuile est de 15 Mo. Autrement dit, huit tuiles de cache RAMBO donnent à l'accélérateur un total de 120 Mo de cache supplémentaire. Chaque tuile de ce cache est connectée par un bus de 1,3 To/s. En comparaison, les tuiles de calcul Ponte Vecchio sont combinées avec les tuiles de base avec un bus de 2,6 To/s.

Quant aux matrices de base, elles contiennent du cache L3 (144 Mo), divers contrôleurs et bus, dont huit contrôleurs de mémoire HBM, un contrôleur PCIe 5.0 à 16 voies ou CXL, un contrôleur de tension (Fully Integrated Voltage Regulator, FIVR) et d'autres alimentation contrôles. La surface d'une dalle de base, qui sera produite à l'aide de la technologie de traitement Intel 7 (10 nm), est de 646 mm2. Il se compose de 17 couches.

Les blocs informatiques Ponte Vecchio sont fabriqués à l'aide de la technologie de traitement 5 nm de TSMC. Ce dernier produit également des tuiles utilisant la technologie 7nm avec un contrôleur Xe-Link. Intel fabrique son propre cache RAMBO et les tuiles de base du package Foveros en utilisant sa technologie Intel 7 (10 nm). Lors de l'utilisation du refroidissement par air, le TDP maximal pour le Ponte Vecchio est indiqué à 450 watts. Cependant, lors de l'utilisation du refroidissement liquide, ce chiffre atteint 600 watts. La plage de température de fonctionnement indiquée est de 65 à 81 °C.

La surface totale des 47 tuiles actives est de 2330 mm2. Avec 16 tuiles thermiques, il passe à 3100 mm2. Dans le même temps, la surface totale de l'ensemble de l'accélérateur Ponte Vecchio dans le boîtier, qui est connecté au système à l'aide de 4468 contacts, est de 4844 mm2. Le nombre total de transistors est supérieur à 100 milliards.

2022-02-22 16:07:25

Auteur: Vitalii Babkin