Commercial Times によると、TSMC は来月、3nm (N3) チップの量産を開始する予定です。 N3 プロセスに基づく最初の製品の TSMC 顧客への納入は、来年初めに予定されています。

通常、TSMC は春に新しいプロセス技術の大量生産を開始し、通常は 9 月にリリースされる Apple の新しい iPhone モデルの発売に間に合うように十分なチップを生産します。ただし、N3 ノードの開発には通常よりも時間がかかりました。そのため、Apple は将来のスマートフォンで異なるプロセス技術を使用する予定です。それにもかかわらず、Apple は 3nm プロセス技術を使用して製造されたチップを受け取る最初の TSMC 顧客になります。

5nm N5 テクノロジーと比較して、N3 テクノロジーは同じレベルの消費電力を維持しながら周波数を 10 ~ 15% 向上させるか、周波数を維持しながら水晶の消費電力を 25 ~ 30% 削減します。また、新しい生産基準により、チップ上のトランジスタの密度を約 1.6 倍にすることが可能になります。

N3 ノードの主な機能の 1 つは FinFlex テクノロジです。これにより、顧客にとって同社のチップの魅力が高まるはずです。この技術の本質は、メーカーが単一の半導体結晶内で異なるタイプのFinFETトランジスタを使用できるようにすることです。このテクノロジーは、CPU や GPU などの複雑な製品に役立ちます。したがって、Apple、AMD、Intel、および NVIDIA は、特定のコンピューティング タスクに対してより生産的なソリューションをリリースできるようになります。

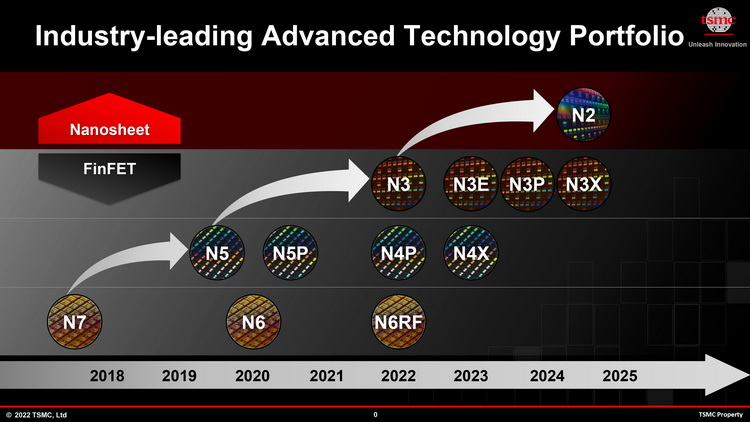

今後、TSMC は N3E、N3P、および N3S プロセス技術を発表します。最初の 1 つは N3 の最適化で、最後の 2 つはさまざまなアプリケーション クラスの N3E の最適化です。 N3P は高性能チップに焦点を当てていますが、N3S はトランジスタ密度を高めたエネルギー効率の高いチップに焦点を当てています。両方のプロセスは 2024 年に開始される予定で、N3E は 2023 年に開始されます。

2022-08-18 13:42:27

著者: Vitalii Babkin