Dans le monde moderne des processeurs, il n'est plus surprenant de trouver une autre vulnérabilité, et parfois des technologies conçues à l'origine pour augmenter le niveau de sécurité deviennent un chemin pour un attaquant. Un certain nombre de chercheurs pensent à juste titre qu'il ne sera pas possible de se débarrasser des « patchs » et qu'il faut changer les principes profonds qui sous-tendent les architectures de processeurs.

L'un de ces projets, développé depuis 2010 par SRI International et l'Université de Cambridge, est CHERI. Arm a rejoint en 2019, dévoilant récemment le premier prototype de carte Morello basé sur deux des principes fondamentaux de CHERI de compartimentation évolutive et de protection fine du contenu de la mémoire. Les deux principes sont implémentés dans le matériel et ne sont pas nouveaux en eux-mêmes.

En fait, nous parlons d'une extension du jeu d'instructions standard, à l'aide de laquelle même écrit en utilisant des langages qui permettent de faire relativement facilement des erreurs lors de l'utilisation de la mémoire (et c'est généralement C / C + +), les logiciels peuvent fonctionner sans créer de graves failles de sécurité. Une compartimentation prudente (c'est-à-dire une séparation) du code du système d'exploitation et des applications, bien qu'elle n'exclue pas la présence de vulnérabilités, mais limite sérieusement la zone de dommages possibles.

En particulier, toute instruction de chargement/mémorisation et toute opération de récupération doivent être autorisées matériellement par le processeur. Bien sûr, il ne s'agit pas d'une protection de haut niveau, mais plutôt d'un ensemble d'éléments de base pour en construire une. Le principe de cloisonnement est encore plus simple : si dans une architecture classique un attaquant peut prendre le contrôle de l'ensemble du système, alors dans des OS et applications isolés les uns des autres, il ne pénétrera que dans une des nombreuses petites « cellules », et ses actions servir de signal aux mécanismes de défense.

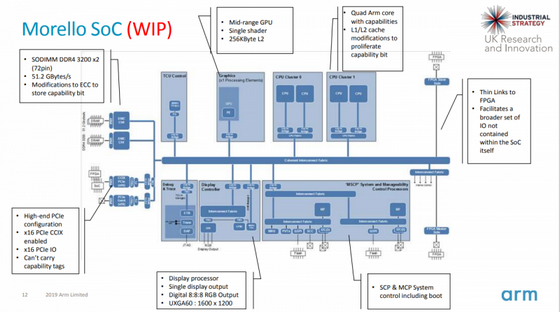

Arm Morello est la première puce basée sur CHERI. L'implémentation matérielle actuelle utilise des cœurs Neoverse N1 (ARMv8.2) modifiés cadencés à 2,5 GHz. Les premières cartes avec le nouveau processeur sont destinées aux géants de l'informatique tels que Google et Microsoft, ainsi qu'aux établissements d'enseignement intéressés. À l'heure actuelle, les développeurs proposent un noyau FreeBSD modifié, faisant partie des programmes UNIX standard, ainsi que d'autres applications. Avec l'avènement des cartes et des processeurs prêts à l'emploi, le processus d'adaptation du logiciel devrait être considérablement accéléré.

2022-01-25 07:10:31

Auteur: Vitalii Babkin